岳宇轩:中国海洋大学计算机组成原理实验-32位加法器设计与仿真

需积分: 0 3 浏览量

更新于2024-08-05

收藏 495KB PDF 举报

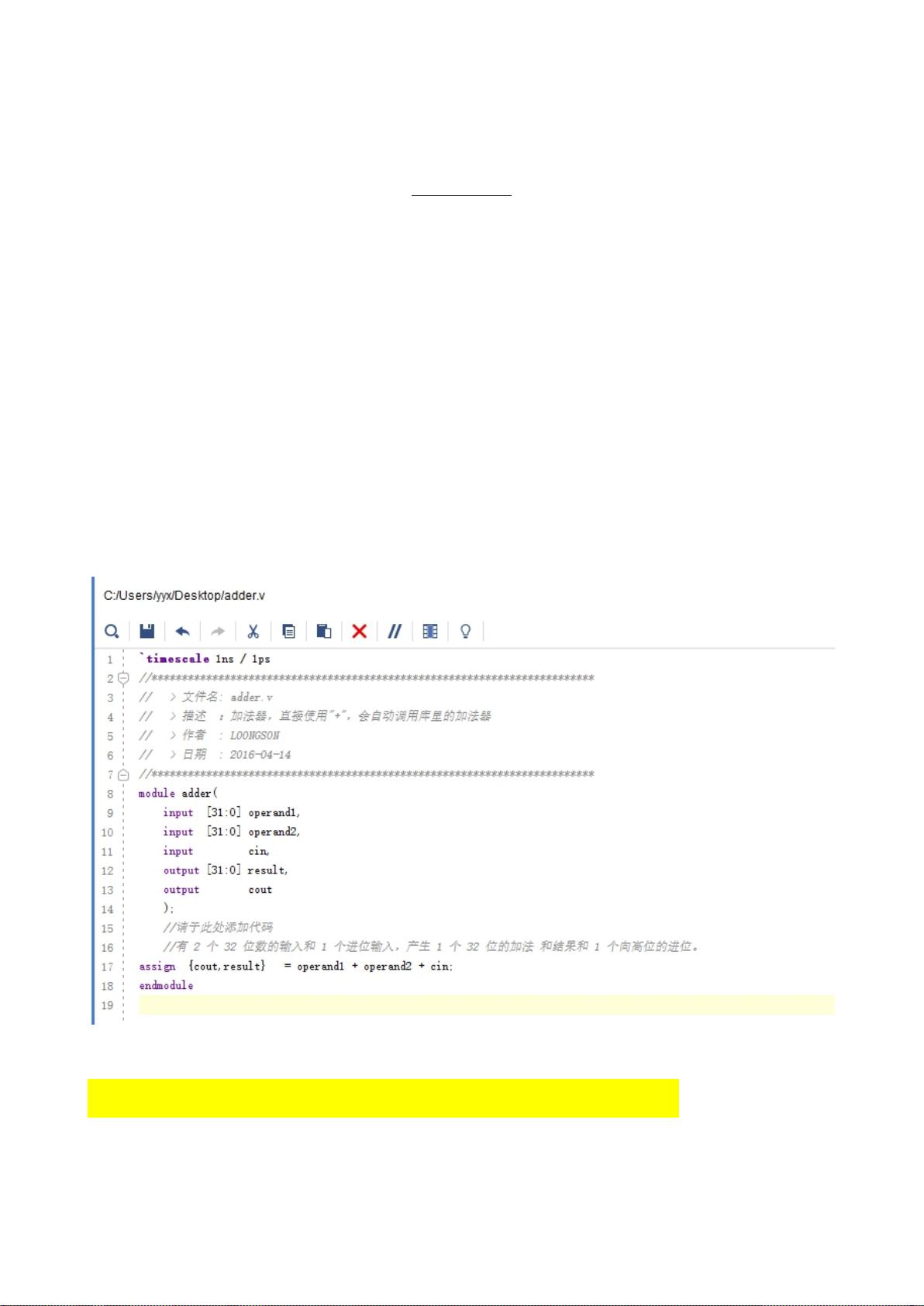

本篇实验报告是关于中国海洋大学计算机科学与技术系2019级学生岳宇轩在2021年4月12日进行的计算机组成原理课程中的加法器设计与实现。实验主要围绕Verilog语言编写硬件描述代码以及使用SystemVerilog进行测试bench的设计。

首先,实验的核心内容是实现一个32位的加法器,该加法器接受两个32位输入(operand1和operand2)和一个进位输入(cin)。代码片段中,通过`assign`语句,将输入的两个操作数加上cin的结果分配给`result`和`cout`,实现了加法运算的功能。这种设计确保了无论操作数如何变化,加法都会实时计算并在指定延迟后更新输出。

接着,实验者构建了一个名为`testbench.v`的测试模块,利用`timescale`关键字设置仿真时间和精度。在这个模块中,定义了输入和输出的寄存器,如`operand1`、`operand2`、`cin`、`result`和`cout`。然后,通过`always`循环和`$random`系统任务,设置了输入值的随机性,以便于测试加法器对不同输入的反应。特别地,`cin`被设置为每次循环的随机数除以2的余数,模拟实际的进位情况。

在仿真阶段,实验者选择了两个特定的输入值d8ace2b1和2ac2d555,以及一个低位进位(cin)。预期的计算结果是32位的加法结果036fb807。通过观察仿真波形图像,可以验证加法器是否按照预期正确处理了输入并生成了正确的输出。

总结来说,这次实验涉及到的知识点包括硬件描述语言(如Verilog)在设计数字逻辑电路中的应用,如加法器的实现;系统级设计方法,通过testbench进行功能验证;以及随机数生成和仿真测试的技巧。理解和掌握这些概念对于深入理解计算机组成原理和数字逻辑设计至关重要。通过实际操作和分析,学生能够提升对计算机硬件工作原理的直观认识和编程技能。

2022-08-03 上传

2022-08-03 上传

2022-08-08 上传

2022-08-08 上传

2022-08-03 上传

2022-08-03 上传

2022-08-08 上传

2022-08-03 上传

2022-08-03 上传

Friday永不为奴

- 粉丝: 22

- 资源: 317

最新资源

- dc-portfolio-site

- liteBox-开源

- c10lp_refkit_zephyr:在C10LP RefKit FPGA板上的litex vexriscv内核上运行的演示Zephyr应用程序

- Tasky

- UpGuard Cyber Security Ratings-crx插件

- 算法:基本算法和数据结构实现

- JQuerygantt,jquery甘特图

- 参考资料-基于RS485和单片机的排队机控制系统设计.zip

- JRDropMenu:JRDropMenu可快速实现下拉菜单功能

- 源代码深度学习入门:基于Python的理论与实现

- HUPROG:一个包含HUPROG'17(Hacettepe大学编程竞赛)的问题和该问题的解决方案的回购

- Spotify-Data:扩展下载Spotify数据时提供的基本流历史记录数据

- 编码方式

- simple.rar_按钮控件_Borland_C++_

- lua-table:具有超能力的lua表

- bitwarden-menubar:macOS菜单栏中的Bitwarden