Xilinx Zynq UltraScale+ MPSoC FZ3A开发板原理图解析

需积分: 50 64 浏览量

更新于2024-07-15

收藏 356KB PDF 举报

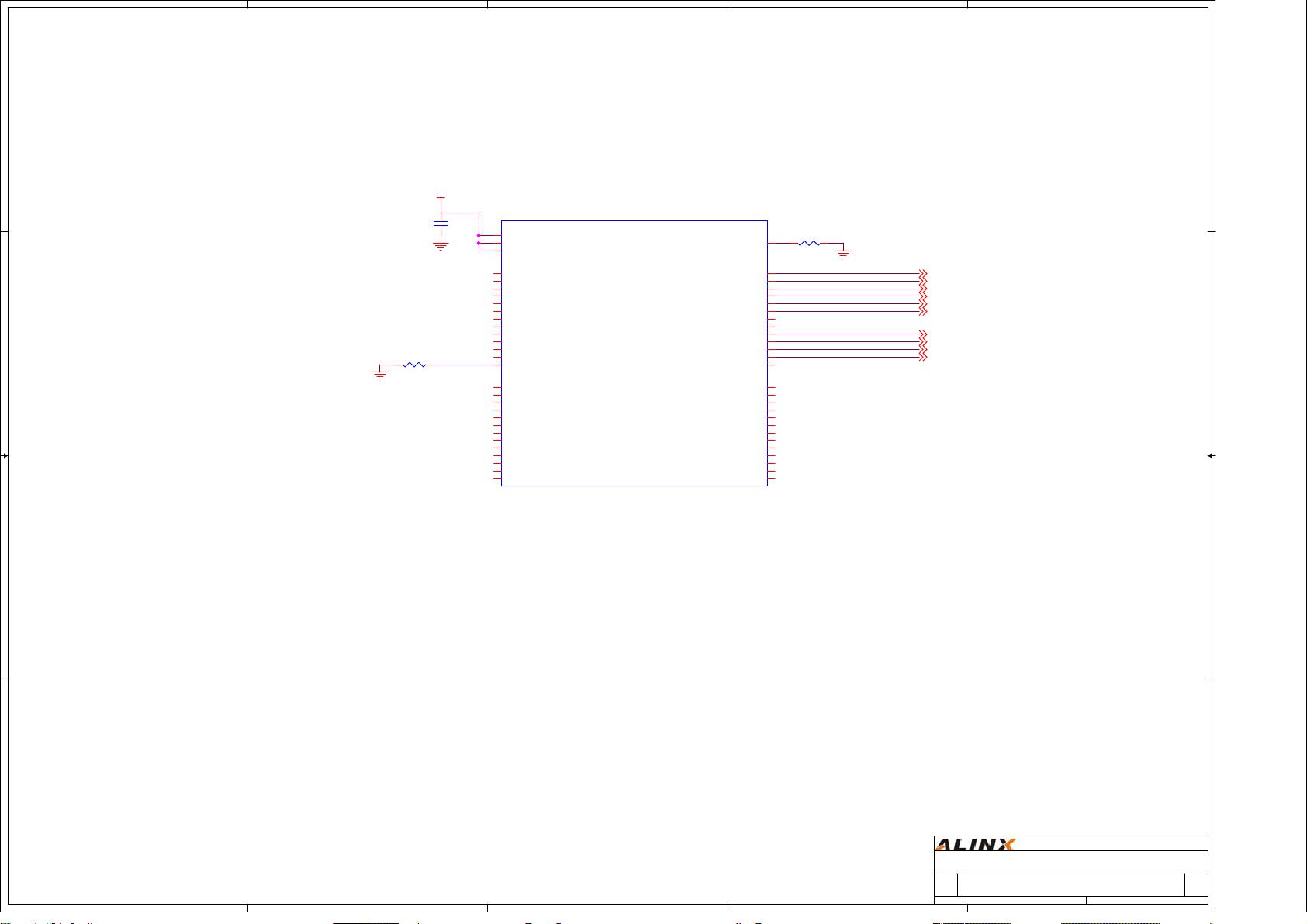

“FZ3A原理图.pdf”是关于edgeboard lite FZ3A开发板的电路设计文档,其中详细阐述了开发板的硬件配置和接口布局。该开发板基于Xilinx公司的Zynq UltraScale+ MPSoCs EG系列芯片XAZU3EG-1SFVC784I,具有强大的处理能力和丰富的外设接口。

FZ3A开发板的核心是Xilinx的Zynq UltraScale+ MPSoC,这是一款高度集成的系统级芯片(SoC),集成了可编程逻辑(PL)和处理系统(PS)。PS部分搭载了两片2GB的DDR4内存,每片32位宽,以及一片8GB的eMMC Flash存储和256Mb的QSPI Flash,提供了高效的数据处理和存储能力。

开发板的外围接口设计十分丰富,包括:

1. 两个USB接口,一个是USB3.0,另一个是USB2.0,满足高速数据传输需求。

2. 一个MINI DP接口,用于高清视频输出。

3. 千兆以太网接口,支持快速网络连接。

4. USB串口,方便进行调试和通信。

5. PCIE接口,提供高速外部设备扩展能力。

6. TF卡接口,便于添加额外的存储空间。

7. 44针扩展口,可以连接各种扩展模块。

8. MIPI接口,适用于摄像头和其他MIPI兼容设备。

9. BT1120接口,可能用于视频处理或传输。

10. 按键和LED,用于用户交互和状态指示。

文档中的Blockdiagram部分可能展示了这些组件在开发板上的物理布局和信号连接关系。例如,BOOTMODE引脚用于设置启动模式,可以选择不同的启动设备如QSPI、SD卡或eMMC。此外,还有PSJTAG接口,用于对PS部分进行调试。其他如PS_POR_B、PS_SRST_B、PS_REF_CLK_503等信号线,分别对应电源复位、系统复位和时钟信号,这些都是确保系统正常运行的关键信号。

FPGA的相关引脚如FPGA_DONE、FPGA_TDO、FPGA_TCK、FPGA_TMS和FPGA_TDI,用于FPGA的配置和测试。PS部分的错误输出和状态引脚(PS_ERROR_OUT、PS_ERROR_STATUS)则用于故障诊断。

FZ3A开发板是一个功能强大的平台,适合进行嵌入式系统开发、硬件原型验证、算法测试等多种应用。其小巧的体积和丰富的外设使其在教育、研究和工业应用中具有广泛的应用前景。开发者可以通过理解这份原理图,深入了解开发板的工作原理,并进行相应的软件和硬件定制。

2020-06-12 上传

2021-12-20 上传

2020-06-12 上传

2019-09-16 上传

2019-09-22 上传

2021-10-10 上传

2023-08-16 上传

iversn

- 粉丝: 2

- 资源: 5

最新资源

- 编译器2

- 电子功用-多层陶瓷电子元件用介电糊的制备方法

- JLex and CUP Java based Decompiler-开源

- 管理系统系列--自动发卡系统(包含前台以及后台管理系统),对接payjs支付(无须企业认证).zip

- 整齐的块

- goit-markup-hw-03

- (课程设计)00.00-99.99 数字电子秒表(原理图、PCB、仿真电路及程序等)-电路方案

- DiskUsage.0:适用于 Android 的 DiskUsage 应用程序

- HonorLee.me:我的Hexo博客

- DZ3-卡塔琳娜·米尔伊科维奇

- 管理系统系列--智慧农业集成管理系统.zip

- 毕业设计:基于Java web的学生信息管理系统

- (资料汇总)PCF8591模块 AD/DA转换模块(原理图、测试程序、使用说明等)-电路方案

- CampaignFinancePHL:使费城的竞选财务数据更易于理解

- Week09-Day02

- JiraNodeClient:用于从Jira导出导入数据的NodeJS工具