Cadence PCB仿真全攻略:从设置到分析

需积分: 16 49 浏览量

更新于2024-07-27

收藏 465KB PDF 举报

Cadence PCB仿真是一种关键的电子设计自动化(EDA)工具流程,用于模拟和验证印制电路板(PCB)的设计性能。本文将详细介绍 Cadence SI(Signal Integrity)仿真的步骤,确保电路板在实际应用中的信号完整性。

首先,准备工作至关重要。在Allegro PCB设计软件中,有三种方式可以进行SI仿真:直接在画板界面操作,通过SpecctreQuest打开*.brd文件并进行设置,或者在SigXplore程序中创建拓扑进行仿真。在开始之前,确保你的PCB设计已经完成,并且地线、电源电压设置正确,以满足阻抗要求。

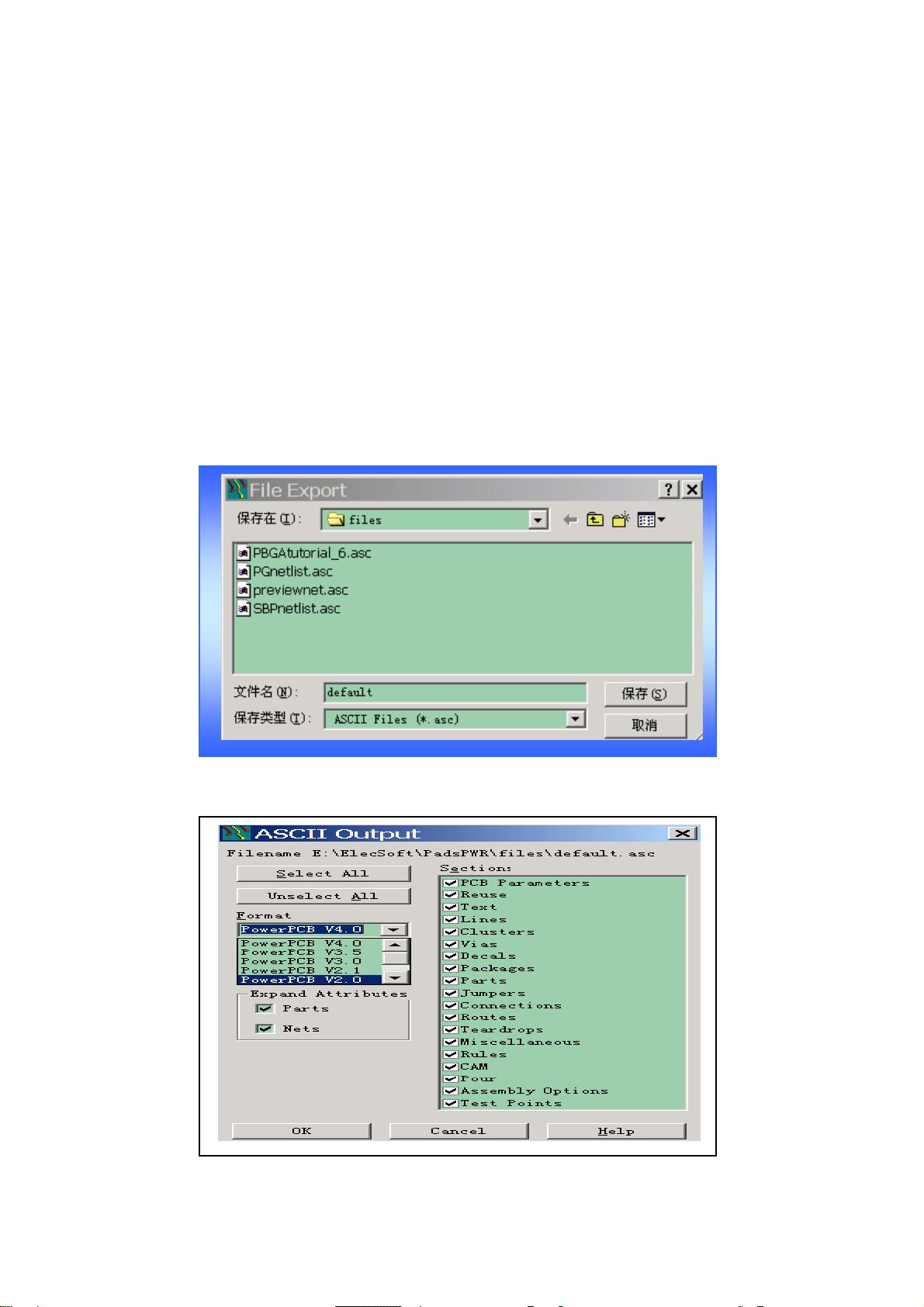

从PowerPCB到Allegro的转换是必不可少的步骤。用户需在PowerPCB中导出ASCII格式的*.asc文件,选择包含零件和网络的详细信息。在导出时要注意选择PowerPCB V3.0及以下版本的格式,以避免导入问题。随后,在Allegro中通过Import功能,选择PADS选项,配置源asc文件路径、pads_in.ini文件路径以及转换后的文件保存位置。

接下来,设置必要的参数,如源文件目录、pads_in.ini文件位置和目标文件夹,运行转换过程,生成新的PCB布局文件。这个过程将把PowerPCB设计转换为Allegro能够识别的格式,以便进行后续的仿真。

在Allegro中,用户需使用Probe功能来指定需要仿真的信号线,这一步对于准确模拟信号传输至关重要。然后,设置仿真参数,包括但不限于信号频率范围、噪声水平、电源模型等,这些参数直接影响到仿真结果的精确度。

进行仿真后,会生成包含各种参数的仿真结果报告,包括但不限于信号衰减、反射、串扰等指标。根据需要,可以更改电路条件,如电源电压变化或不同负载,进行多次重复仿真,以获得更全面的性能数据。

最后,电气约束规则的定义不容忽视。这包括信号完整性约束(SI constraints)、电源完整性约束(PI constraints)和其他相关规则,以确保电路设计满足预期的电磁兼容性和信号质量标准。

整个Cadence PCB仿真流程旨在提供设计师一个完整的工具链,帮助他们在设计阶段发现潜在的问题,优化信号传输性能,从而减少后期调试的成本和时间。通过遵循以上步骤,工程师可以确保他们的PCB设计在实际应用中具有良好的信号完整性,提高整体系统的性能和可靠性。

496 浏览量

285 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

lyw711

- 粉丝: 0

- 资源: 4