使用SystemVerilog进行时钟域穿越(CDC)设计与验证技术

需积分: 35 155 浏览量

更新于2024-07-20

1

收藏 1.72MB PDF 举报

"跨时钟域(CDC)设计与验证技术使用SystemVerilog"

在复杂的数字系统设计中,尤其是在RTL(寄存器传输级)设计中,处理跨时钟域问题至关重要。时钟域交叉(Clock Domain Crossing, CDC)是指数据在不同时钟域之间传递的情况,这通常涉及到潜在的 metastability(亚稳态)风险,可能导致系统错误或不稳定。这篇文档详细阐述了如何使用SystemVerilog来有效设计和验证跨时钟域的解决方案。

1.0 引言

文档首先引入了跨时钟域设计的重要性,指出在多时钟设计中,必须在CDC边界处谨慎构建,以确保数据的准确传输和系统的可靠性。

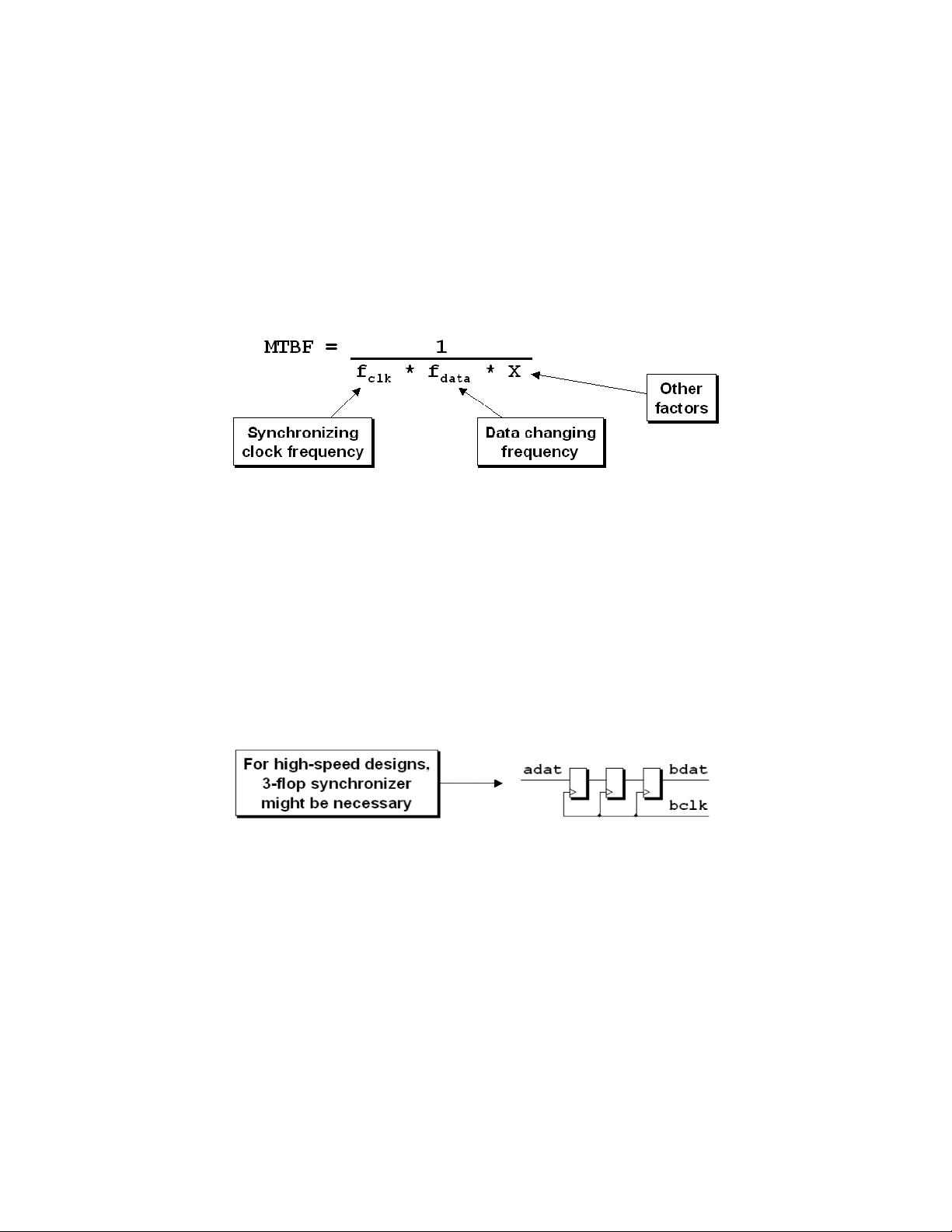

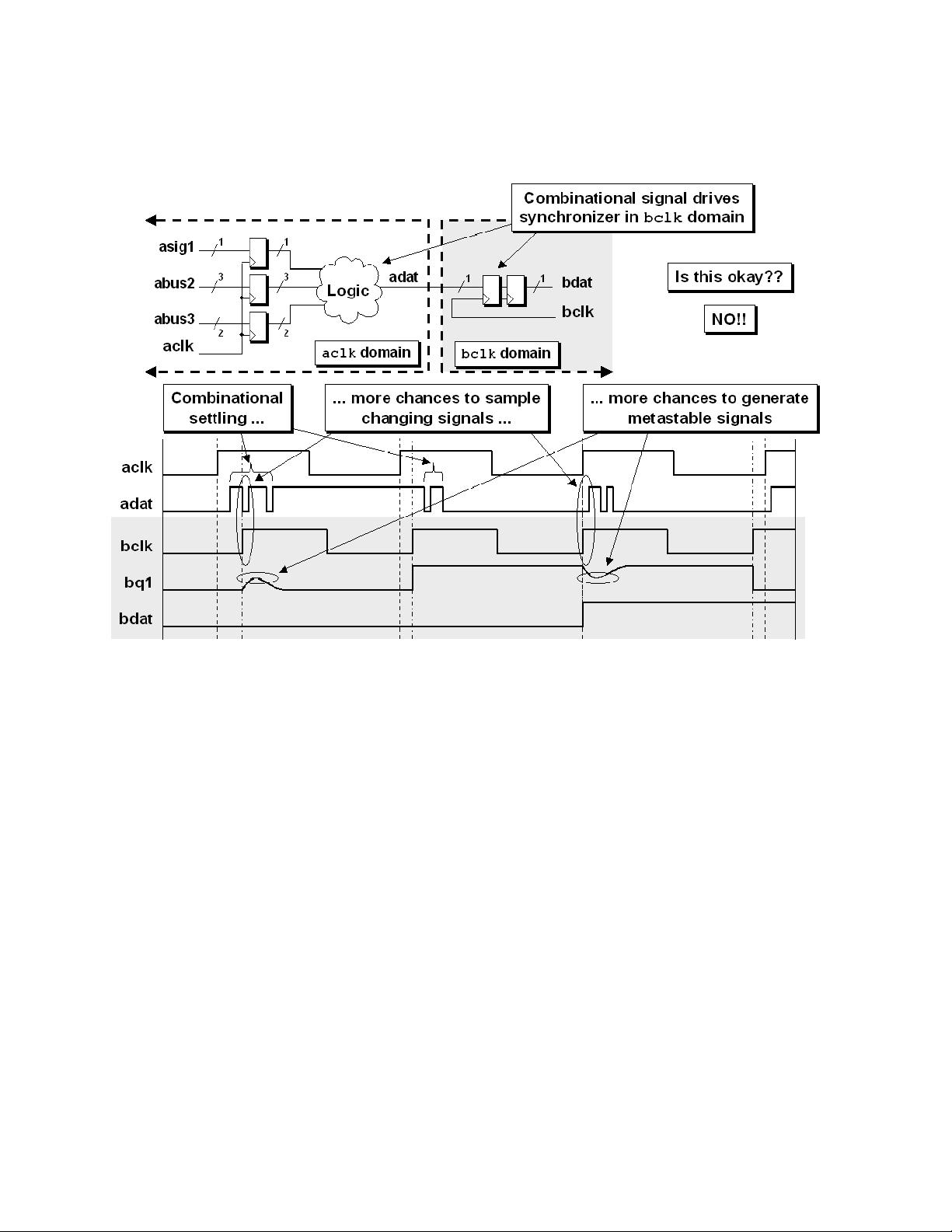

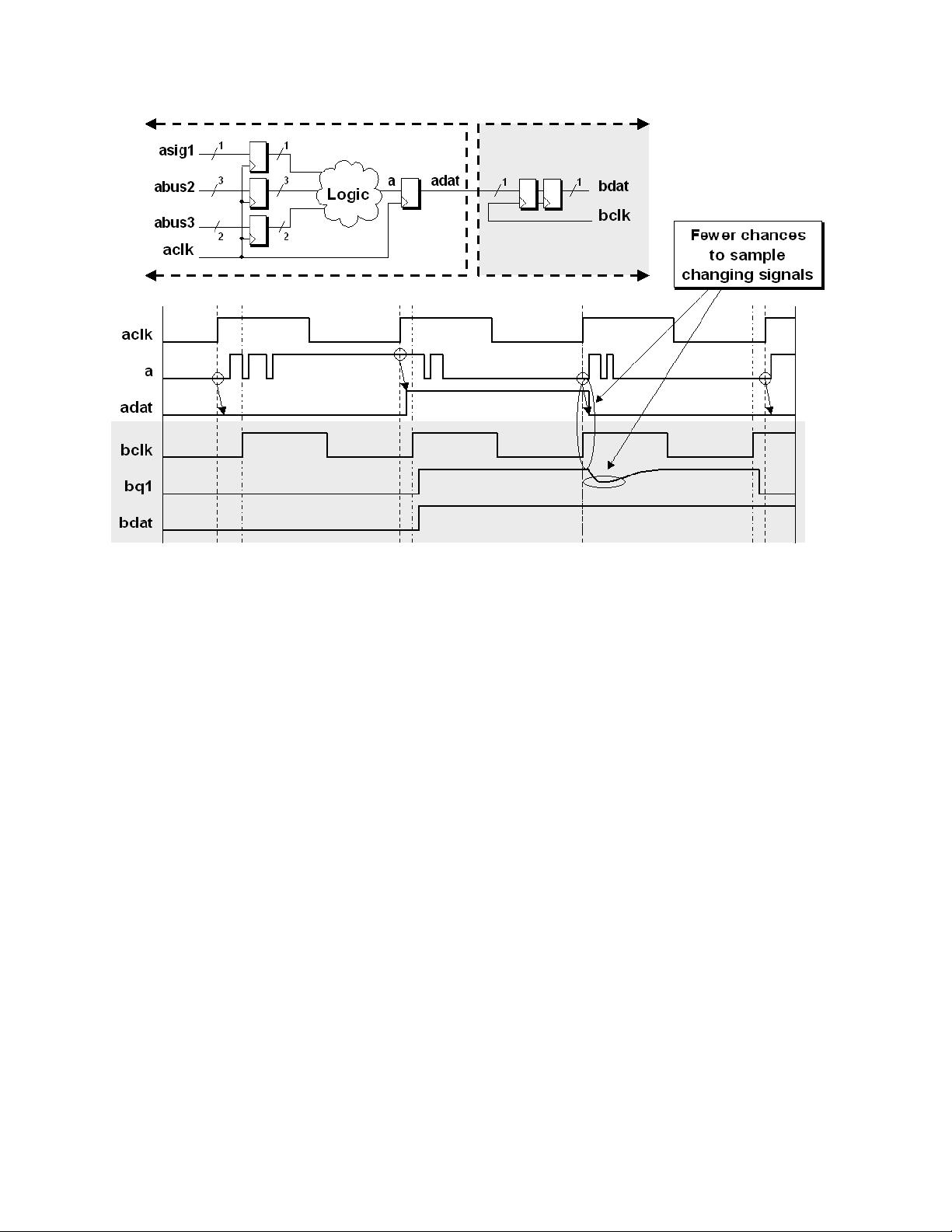

2.0 Metastability

2.1 亚稳态问题

亚稳态是时钟域交叉中的主要挑战,当一个时钟域中的信号在另一个时钟域采样期间处于不确定状态时,就可能发生亚稳态。这种状态可能导致数据错误,因为接收端可能无法正确解析输入信号。

3.0 同步器

3.1 两种同步场景

文档讨论了两种常见的同步策略:同步数据和同步控制信号。同步器用于解决亚稳态问题,它们通常是基于多级触发器的结构,通过多个时钟周期确保数据稳定。

3.2 双级FIFO设计

文档中提到了一个有趣的双级FIFO设计,用于在不同时钟域间传递多个控制信号。FIFO(First In First Out)结构提供了一种安全的数据缓冲方式,可以避免亚稳态并确保数据的正确同步。

4.0 CDC验证技术

除了设计方法外,文档还强调了验证的重要性。在实现过程中,验证确保了所有CDC路径都已适当地处理,避免潜在的错误。使用SystemVerilog可以实现高级的验证方法,如UVM(Universal Verification Methodology)中的CDC验证组件。

5.0 SystemVerilog的优势

尽管跨时钟域的设计方法可以用任何硬件描述语言实现,但文档中展示了使用SystemVerilog进行高效设计和验证的例子。SystemVerilog提供了更强大的语言特性,如接口、任务、函数以及并发机制,这些都有助于简化复杂CDC设计的实现和验证。

6.0 结论

通过深入理解亚稳态,采用有效的同步器设计,并利用SystemVerilog的高级功能,设计师可以创建可靠且易于验证的跨时钟域解决方案。这篇文档详细阐述了这些技术和最佳实践,为多时钟设计者提供了宝贵的指导。

文档的其余部分可能包括更多具体的设计实例、同步器的实现细节、验证流程的步骤以及其他SystemVerilog工具和技巧,这些都是确保跨时钟域设计成功的关键要素。

2019-08-09 上传

2011-05-21 上传

2021-07-07 上传

2023-06-01 上传

2019-01-21 上传

2024-05-21 上传

2018-09-07 上传

2021-08-27 上传

2014-03-07 上传

futurehome

- 粉丝: 0

- 资源: 2

最新资源

- RSVP协议的多媒体综合服务机制研究

- 计数器实验——数字电路实验

- VB入门教程.asp.doc(入门级哦)

- 51单片机C语言入门教程.pdf

- 46家各大公司笔试题

- JavaScript DOM 编程艺术.pdf

- Keil uv3快速入门.pdf

- 微控制器 (MCU) 破解秘笈之中文有删节版

- GIVEIO IO驱动的源代码

- 微软应用程序架构指南

- C#串口操作串口操作串口操作

- fsadfdsaarkdffasdfdggdd桌面\C++ STL使用手册.pdfASP.NET新闻、论坛、电子商城、博客源码 很经典的php面向对象教程

- C语言上机南开100题(2009年终结修订word版)

- 软件界面设计及编码标准规范

- 总线的简单项排球介绍

- Gzip压缩.docx