74HC109A:双J-K触发器带预设和清除功能

版权申诉

168 浏览量

更新于2024-08-22

收藏 110KB PDF 举报

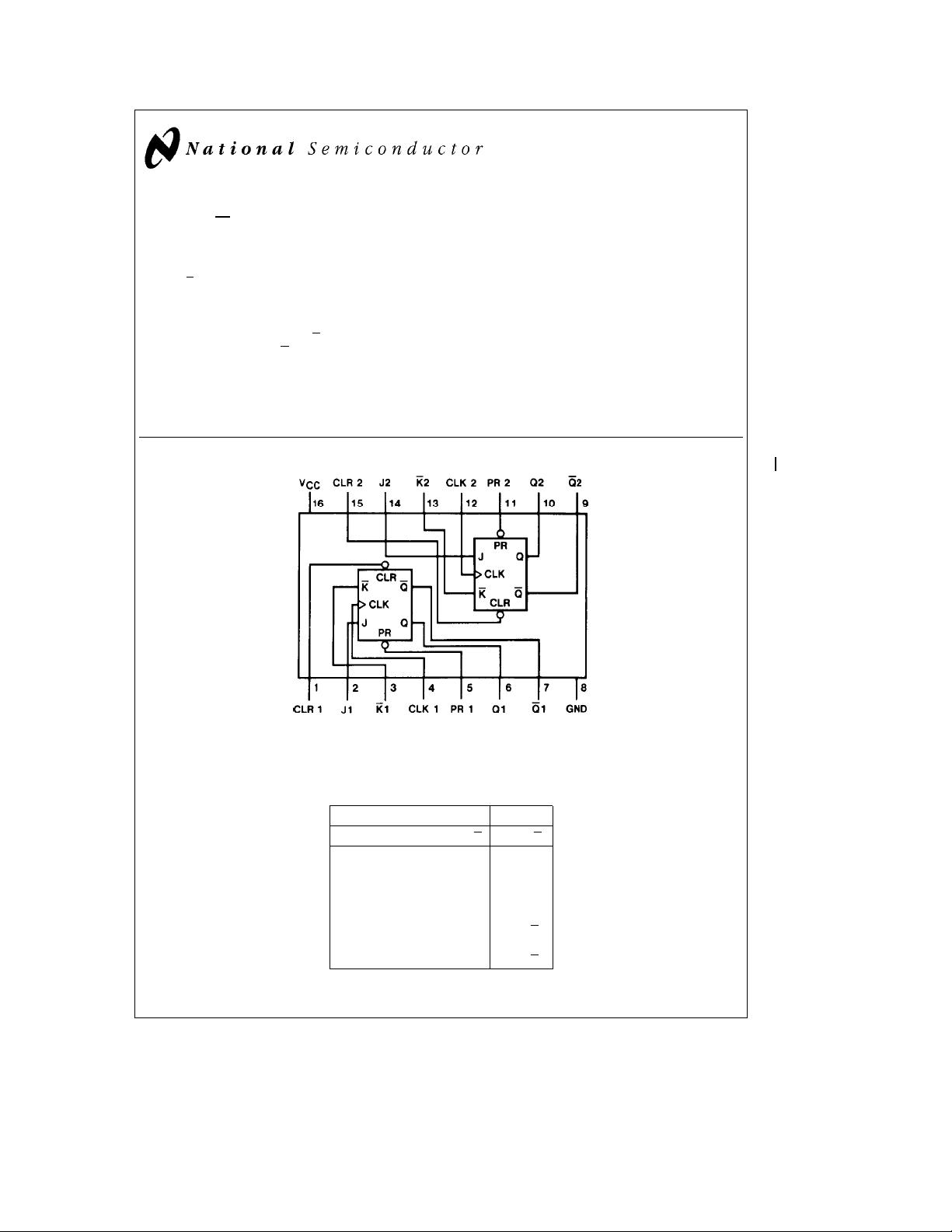

"74HC109A是双J-K触发器集成电路,具有预设和清除功能"

74HC109A是一款基于先进硅门CMOS技术的双J-K触发器,它融合了低功耗消费和高噪声免疫力的特点,同时也具备驱动10个低功耗TTL负载的能力。这款芯片主要由两个独立的J-K触发器组成,每个触发器都有各自的J、K、预设(Preset)、清除(Clear)和时钟(Clock)输入,以及Q和非Q(Q')输出。

1. **触发器结构与工作原理**:

- J-K触发器是一种双输入的边沿触发器,其名称源于输入端的两个字母,J和K。当J=K=1时,触发器会进行翻转(Toggle);J=0,K=1时,Q输出置1(Set);J=1,K=0时,Q输出置0(Reset)。预设和清除输入允许在不受时钟信号影响的情况下直接设置触发器的状态。

- 触发器的工作依赖于时钟脉冲的正沿,即在时钟脉冲的上升沿,触发器状态会发生改变。

2. **特性**:

- 快速响应:典型的传播延迟为20ns,这意味着信号从输入到输出的传递速度非常快。

- 宽泛的电源电压范围:支持2V至6V的操作电压,这使得74HC109A能在多种电源环境下稳定工作。

- 低输入电流:最大输入电流为1mA,这减少了对电源的需求并提高了效率。

- 低静态电流:在74HCS系列中,静态电流最大为40mA,降低了待机时的能耗。

- 强大的驱动能力:每个输出可以驱动10个低功耗TTL负载,适合大规模逻辑电路设计。

3. **兼容性**:

- 74HC系列与54LS/74LS系列在功能和引脚布局上都兼容,这意味着74HC109A可以在设计中替换54LS或74LS系列的相应器件,无需改动硬件连接。

4. **保护措施**:

- 所有输入端都内置了防静电放电的二极管钳位至VCC和地,以防止输入端因静电而受损。

5. **连接图**:

- 连接图详细说明了各输入和输出引脚的连接方式,对于正确使用74HC109A至关重要,用户需按照图示连接电路,以确保触发器按预期工作。

74HC109A广泛应用于数字电路设计,如存储、计数、定时和数据传输等场合,其高效能和低功耗特性使其成为许多嵌入式系统和数字逻辑设计中的理想选择。了解并熟练掌握74HC109A的特性及工作原理,对于进行复杂数字电路设计具有重要意义。

2014 浏览量

977 浏览量

2023-02-11 上传

2023-02-11 上传

2021-09-26 上传

2021-10-10 上传

1523 浏览量

2023-06-29 上传

2023-06-28 上传

等天晴i

- 粉丝: 5982

- 资源: 10万+

最新资源

- 吉菲探索者

- 保险行业培训资料:地县级地区中端福寿连连销售逻辑

- frontend-react

- IEC101-103-104规约分析程序.rar

- 保险行业培训资料:从需求的角度看产品

- rms-list-gen

- DIU:乌苏里奥大学接口处

- tinyMCE:向 WordPress TinyMCE 添加自定义按钮

- 创维电视酷开系统14U系列8S26刷机应用工具包

- hex-to-rgb:将彩色十六进制值转换为rgb

- my-gridsome-app

- nexus-3.20.1-01-win64.rar

- nwis:对 nw.js GUI API 的 IntelliSense 支持

- materiaFramework:项目构建器,基于html POST请求

- IM Café-开源

- conquer_the_world:【打天下篇】工作知识纪要