基于VHDL的4x4bit查表乘法器嵌入式设计与数码管显示

下载需积分: 9 | DOC格式 | 2.27MB |

更新于2024-07-22

| 46 浏览量 | 举报

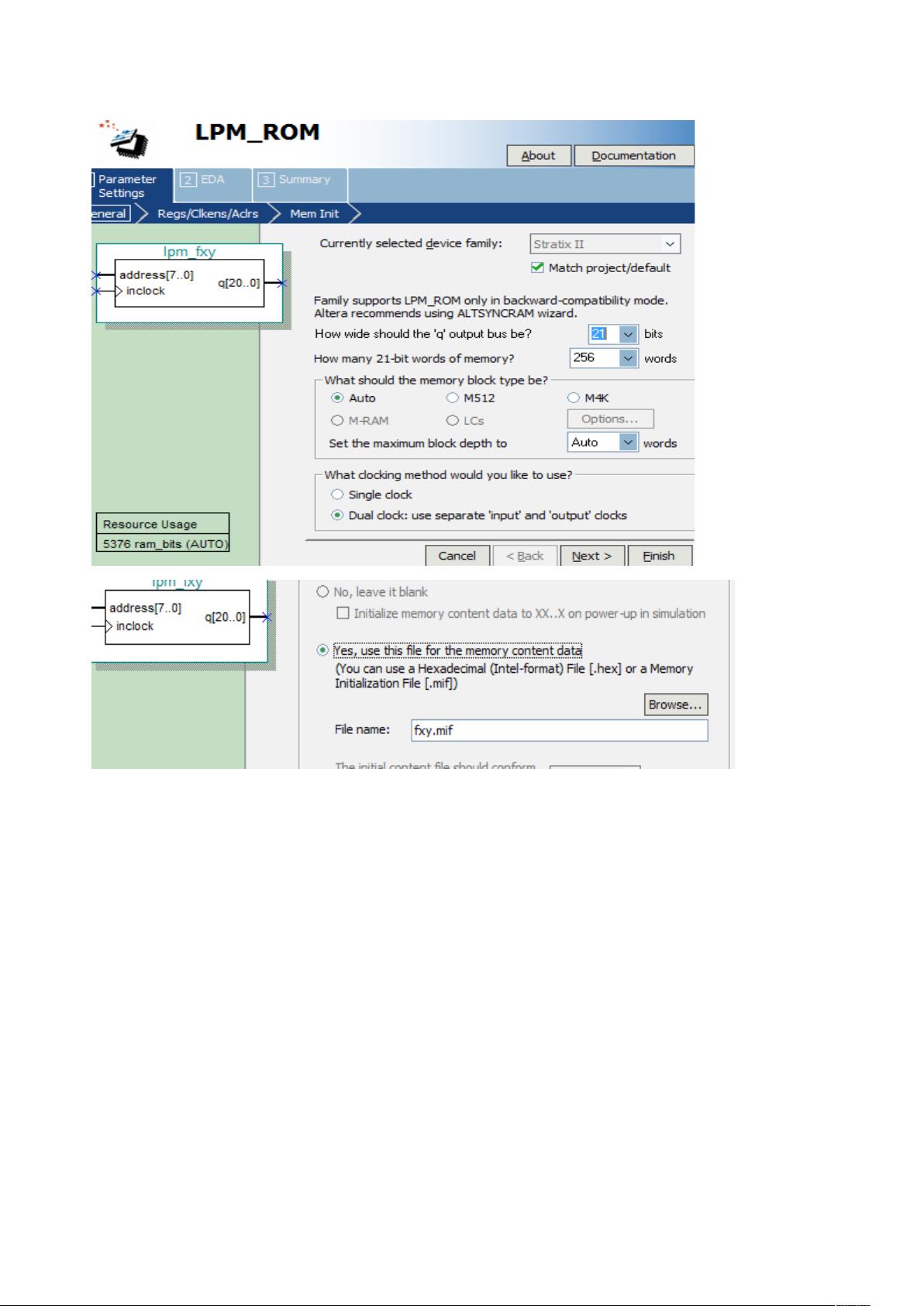

本文主要探讨的是基于嵌入式技术的4x4bit查表式乘法器的设计与实现,使用了VHDL硬件描述语言。设计的核心目标是创建一个高效的硬件乘法器,通过查表的方式处理乘法运算,以提升嵌入式测控系统的运算速度。该乘法器的工作原理是预先计算所有可能的乘积组合,并存储在只读存储器(ROM)中,通过输入数据确定所需的乘积。

设计流程首先要求设计者定义基本的4x4bit乘法器结构,遵循硬件描述语言如VHDL的规则,实现乘法运算的逻辑功能。这包括设计查找表,存储每个输入位对的乘积结果,以及处理时序逻辑以确保正确的运算顺序。此外,设计者还需考虑如何利用输入地址线从ROM中检索出对应的乘积,从而实现实时的运算。

为了验证设计的有效性,项目要求在Xilinx DE2开发板上进行硬件实验。通过连接数码管,设计者编写了7段数码显示译码器程序,用于将乘法器的输出结果显示出来,直观地展示计算结果。同时,利用Xilinx的Signal Tap工具,设计者可以进行实时的仿真波形分析,观察查表式乘法器的实际运算过程,以便于理解和优化性能。

计算精度和数据区域的设定则取决于ROM的容量,设计者可以根据实际需求选择合适的存储空间,以支持不同精度的运算。这种灵活性使得设计适应于不同的应用场景,如工业自动化、嵌入式控制或实时数据处理等。

本文重点介绍了嵌入式系统中的查表式硬件乘法器设计方法,强调了VHDL语言在硬件描述中的应用,以及如何通过DE2开发板和Signal Tap工具进行实际操作和验证。这个项目不仅锻炼了学生的硬件设计能力,也展示了硬件加速在提高系统性能中的重要性。

相关推荐

mengsuixind

- 粉丝: 0

最新资源

- Spring BeanFactory与ApplicationContext的差异解析

- 详细分层注释的JAVA SSH框架搭建教程

- C#实现的职工考勤管理系统源码

- Android动态折线图升级实现与iChartJs的灵活运用

- Java源码学习:在线版JDK源码剖析与实战交流

- C#编程语言速查参考手册

- SkyPlane:使用JavaScript打造的全新小游戏

- 深入解析Android自定义拍照功能与Camera类

- 定制化Docker映像: 熊猫Gix-Docker基于GNU Guix

- 深入解析Spring框架中的配置文件加载机制

- 支付宝API接口开发文档及C#/.NET/PHP实例教程

- 全国IP数据库ACCESS版详细介绍

- Sublime Text 3095 x86绿色版发布

- 深入探索Java线程池与MiniBrowser源码实战

- 掌握GitHub上的CSS属性布局技巧

- OA种子软件管理系统前台功能介绍及使用