3GHz CMOS低噪声放大器的优化设计与关键技术

101 浏览量

更新于2024-08-29

收藏 238KB PDF 举报

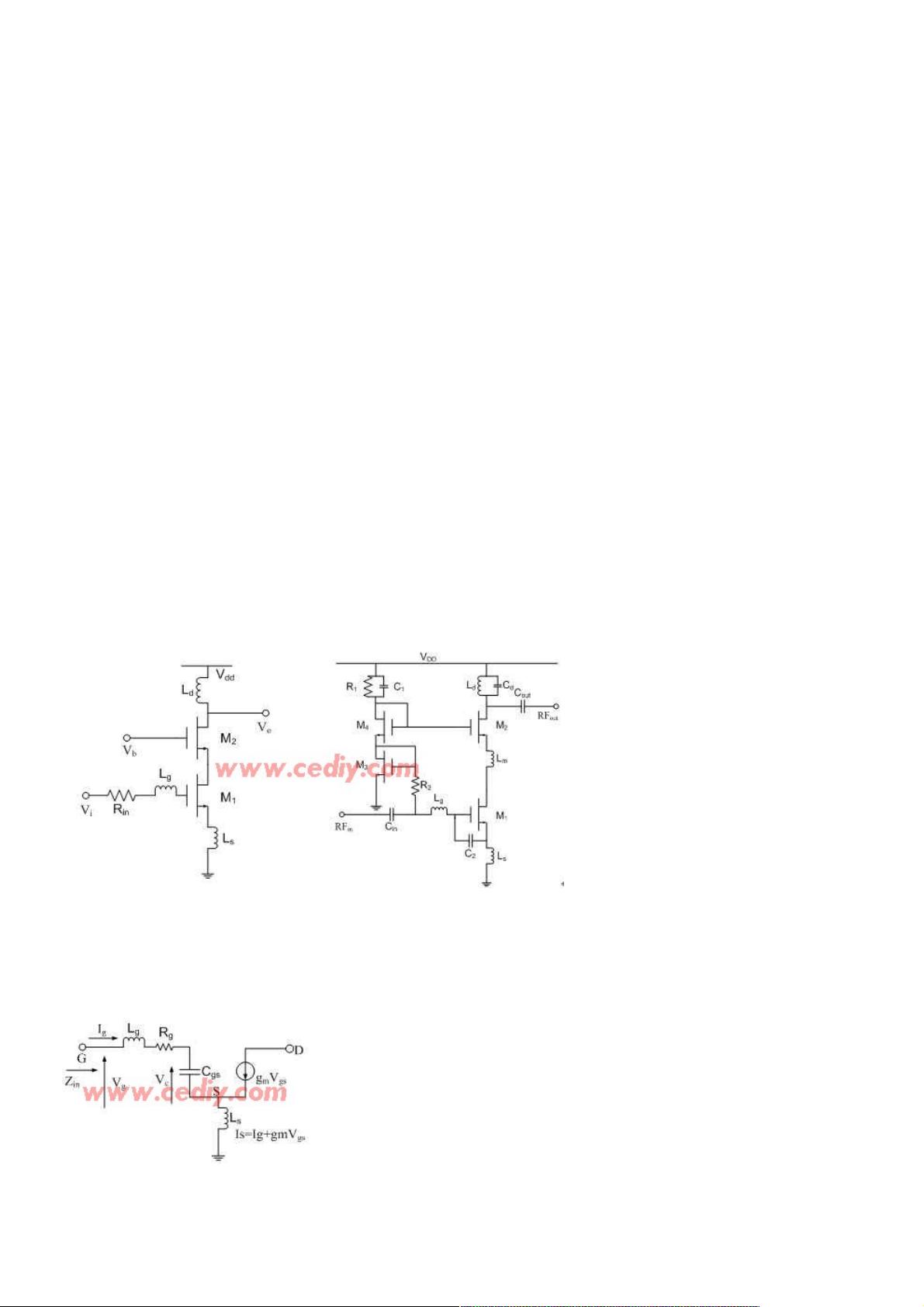

随着现代无线通信技术的快速发展,低成本和便携性的需求推动了CMOS工艺在射频集成电路中的广泛应用。本文主要探讨了一种基于0.18微米CMOS工艺的3GHz低噪声放大器(LNA)的优化设计。低噪声放大器作为无线通信系统射频接收机的基石,其性能对于整体系统的灵敏度和信噪比至关重要。设计的关键在于实现良好的阻抗匹配、低噪声系数(NF)、高线性度以及输入输出的兼容性。

文章采用了共源共栅源极负反馈(CS-CASCODE)结构,这种结构有助于减小噪声并提高放大器的稳定性。设计过程中,作者首先分析了电路的阻抗匹配和噪声性能,通过理论计算和仿真模拟,确定了优化设计策略。结果显示,该LNA表现出优异的性能,包括23.4分贝的功率增益、-25.9分贝的反向传输系数,以及1.1分贝的噪声系数,这些参数确保了接收机在1dB压缩点下的性能达到-13.05分贝毫瓦(dBm)。

关键词“低噪声放大器”、“噪声系数”、“线性度”和“CMOS工艺”强调了设计的核心技术要点,它们是衡量LNA性能的关键指标。此外,文章还强调了CMOS工艺在GHz频率范围内的优势,如成本效益、高集成度和低功耗,这使得基于CMOS的LNA设计在实际应用中更具吸引力。

总结来说,本文通过详细的电路设计和优化策略,展示了如何利用0.18μm CMOS工艺实现一款高性能的3GHz LNA,这对于无线通信系统的设计者来说,提供了重要的参考和实践指导。通过这种优化设计,可以在满足系统需求的同时,兼顾了成本、功耗和性能的平衡,为未来的无线通信设备的发展奠定了坚实的基础。

107 浏览量

146 浏览量

点击了解资源详情

179 浏览量

点击了解资源详情

142 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38642864

- 粉丝: 2

- 资源: 899

最新资源

- easypanel虚拟主机控制面板 v1.3.2

- Coursera

- wind-js-server:用于将Grib2风向预报数据公开为JSON的服务

- 生命源头论坛 LifeYT-BBS V2.1

- TUTK_IOTC_Platform_14W42P2.zip TUTK IOTC官方sdk

- WeatherJournalApp

- 电商小程序源码项目实战

- 美女婚纱照片模板下载

- GB 50231-1998 机械设备安装工程施工及验收通用规范.rar

- MPT-开源

- facebook-archive:使用Facebook的存档数据可以享受一些乐趣

- 阿普奇工业显示器PANEL2000.zip

- action_react

- Torus-开源

- 应用js

- WPF将控件中的文字旋转.zip