高速PCB设计基础与信号完整性分析

需积分: 0 65 浏览量

更新于2024-07-28

收藏 5.23MB PDF 举报

“高速PCB基础理论及内存仿真技术.文字版”

本文档主要介绍了高速PCB设计的基础理论和内存仿真的关键知识点,适用于电子工程师和相关领域的专业人士。高速PCB设计是现代电子设备中不可或缺的部分,它涉及到信号完整性和电磁兼容性(EMC)等问题,对于确保系统的稳定性和可靠性至关重要。

首先,文档阐述了高速电路的基本概念,指出随着电路工作频率的提高,传统集总参数电路理论已无法满足设计需求。高速电路设计需要考虑信号在传输线上的行为,包括反射、串扰等现象。设计流程通常包括对问题的识别、分析和解决,以及对相关基本概念的理解,如信号速率、上升时间、时钟周期等。

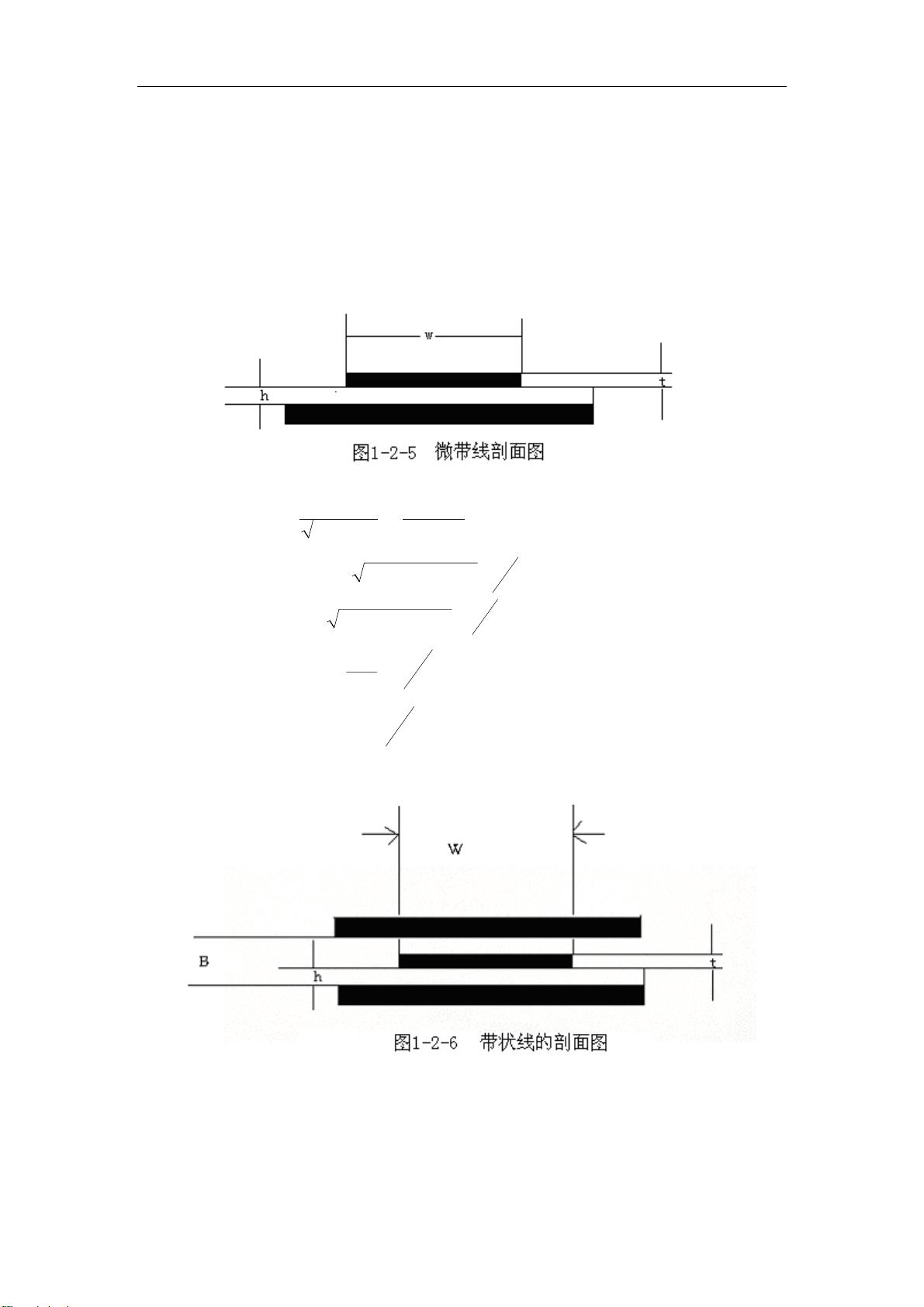

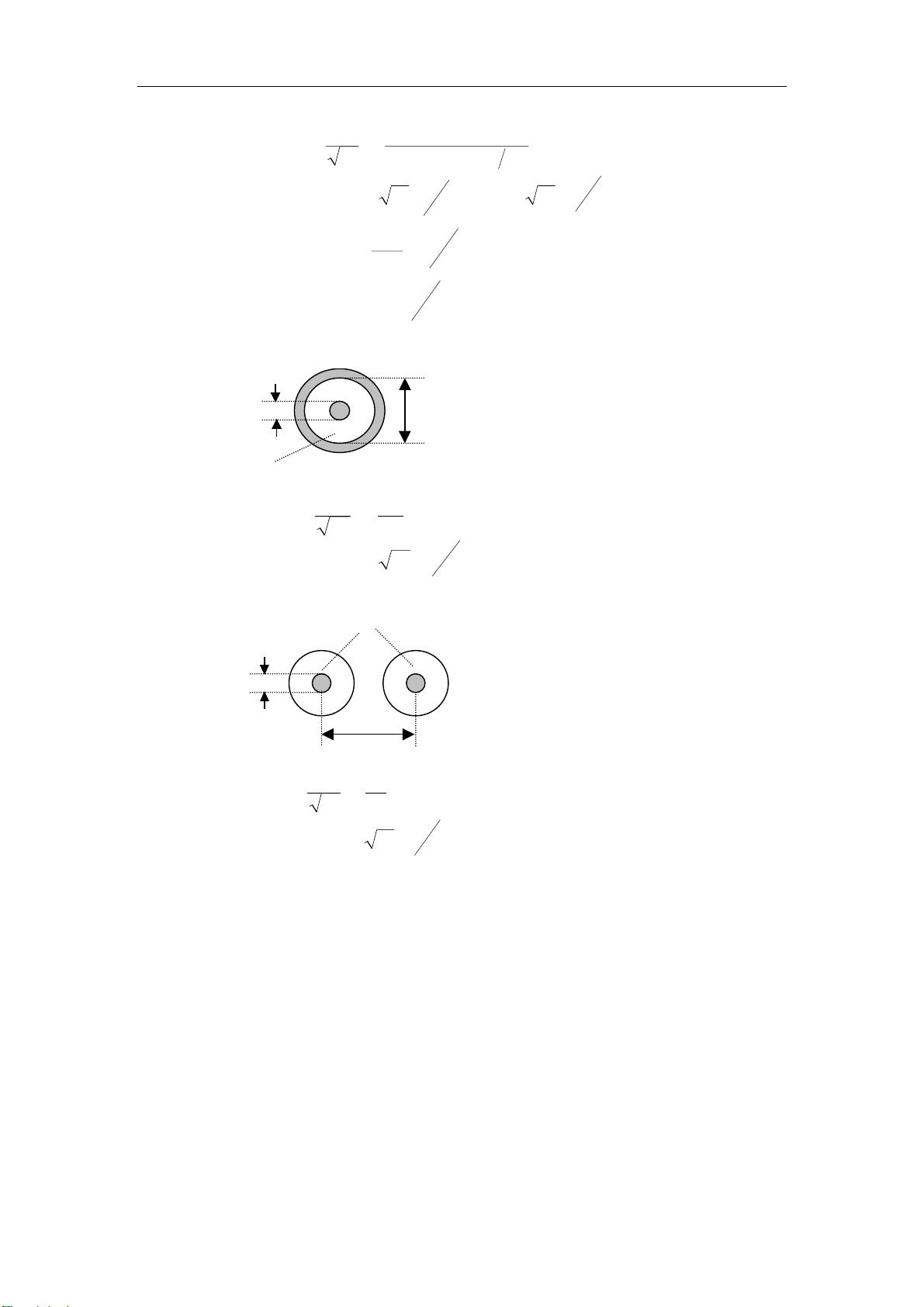

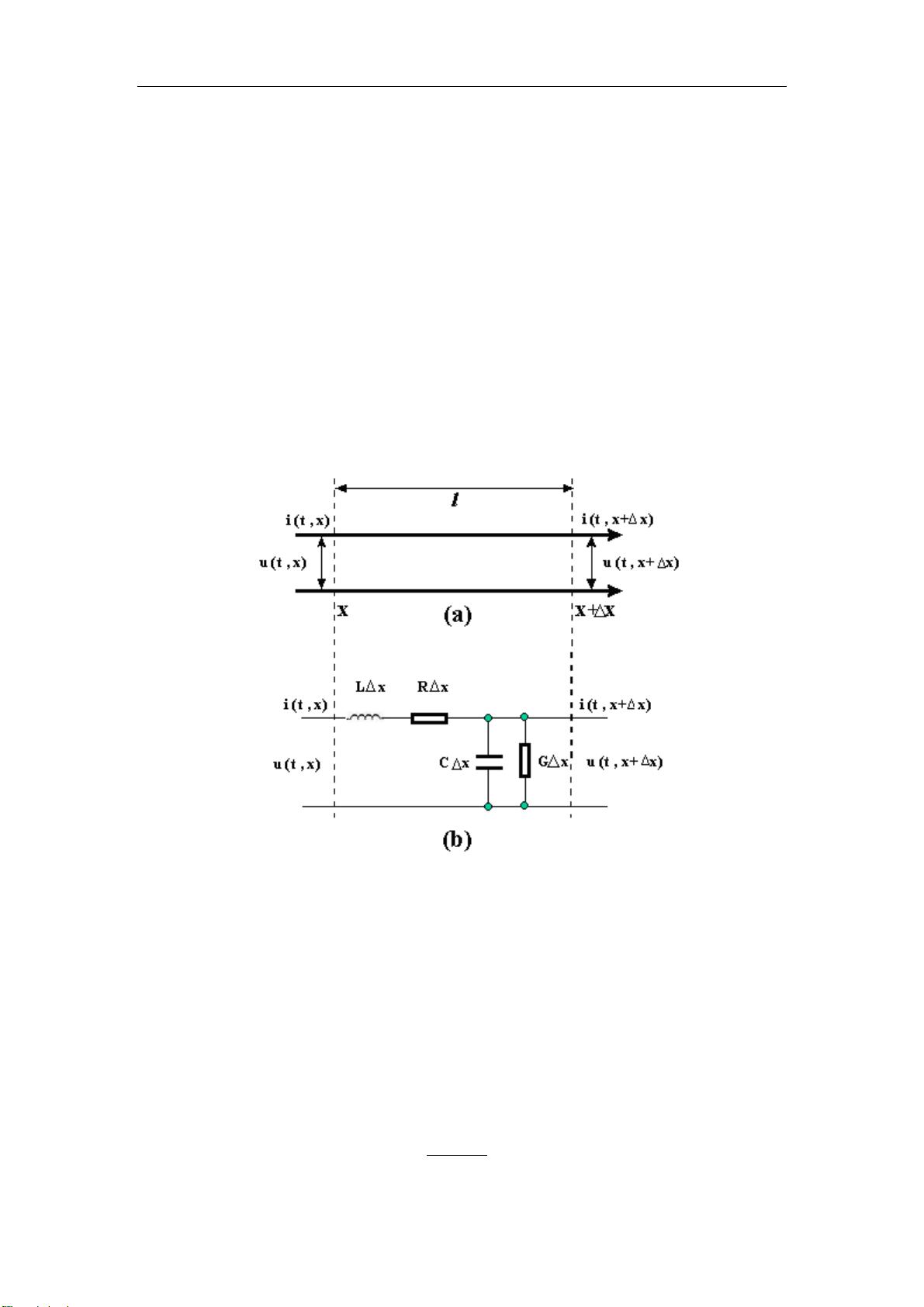

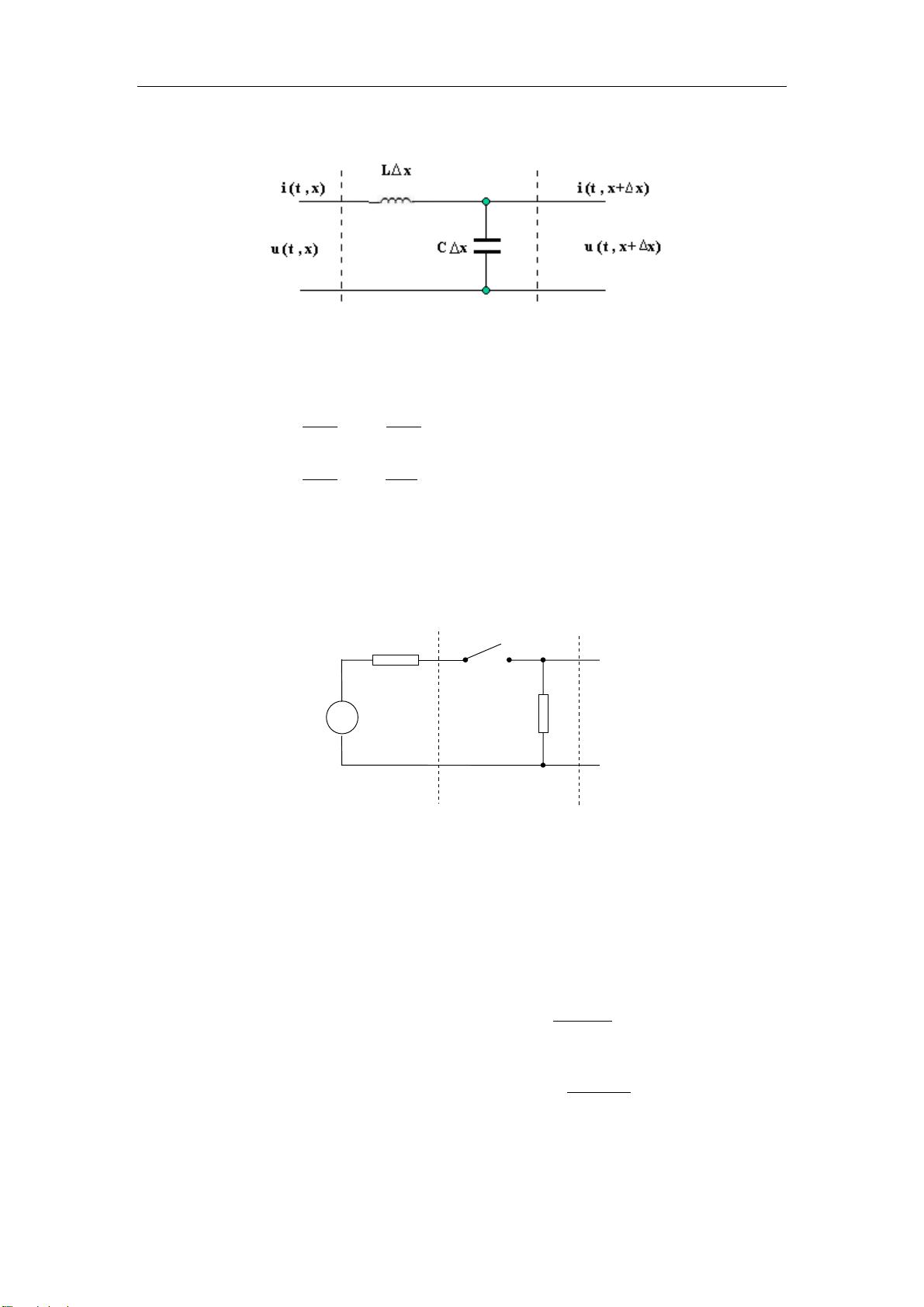

接着,文档深入探讨了传输线理论,讲解了分布式系统与集总电路的区别,以及传输线的RLCG模型和电报方程。传输线的特征阻抗是决定信号质量的关键因素,它决定了信号在传输过程中的衰减和反射。文档详细解释了特性阻抗的计算方法,并讨论了如何通过匹配特性阻抗来减少反射,从而优化信号完整性。

然后,文档详细分析了信号反射的原因和影响,包括过冲、下冲和振荡等问题。反射可能导致信号失真,影响系统性能,因此需要通过串行匹配、并行匹配和差分线匹配等方法进行抑制。

串扰是高速PCB设计中的另一大挑战。文档定义了串扰的基本概念,并区分了前向串扰和后向串扰,讨论了它们的影响机制。此外,还提到了连接器的串扰问题以及如何通过优化布局和布线来降低串扰。

最后,文档涉及了EMI(电磁干扰)的抑制,解释了EMI/EMC的基本概念,分析了EMI的产生原因,如电压瞬变和信号回流。控制EMI的方法包括屏蔽、滤波和接地,其中屏蔽又分为电场、磁场和电磁场屏蔽,而滤波则利用去耦电容和磁性元件来降低噪声。在PCB设计中,合理的叠层设计、传输线RLC参数的选择以及接地策略都是抑制EMI的重要手段。

这份资料提供了高速PCB设计和内存仿真技术的全面介绍,涵盖了信号完整性、传输线理论、串扰分析以及EMI抑制等多个核心主题,对于使用Cadence或其他PCB设计软件的工程师来说具有很高的参考价值。

2015-06-02 上传

2009-07-10 上传

2010-06-26 上传

2023-10-08 上传

2023-08-01 上传

2023-06-26 上传

2023-07-11 上传

2024-04-10 上传

2023-09-19 上传

tyzy200

- 粉丝: 1

- 资源: 8

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常