UVM入门实践:QuestaSim中的C-SV联合仿真教程

"UVM初级开发指南" 是一篇基于张强《UVM1.1应用指南及源代码分析》第一章示例的教程,主要针对初学者介绍了UVM1.1d在QuestaSim环境下的应用。文章作者在2013年10月完成这篇文档,其背景是他在研究生阶段被分配任务使用SystemVerilog开发CPU模型,进行RTL代码的测试,这一过程中他首次接触到了验证技术,并通过阅读《SystemVerilog与功能验证》和张强的书籍深入理解了UVM。

UVM(Universal Verification Methodology),即通用验证方法论,是Verilog自顶向下验证的一种标准方法,它将验证流程划分为多个层次,包括环境(Environment)、接口(Interface)、模块(Module)、组合(Combinational)、时序(Sequential)等组件。在文中,作者重点讲解了如何在C语言和SV语言的联合仿真环境中使用UVM,这对于刚接触验证技术的学生来说,提供了实际操作指导。

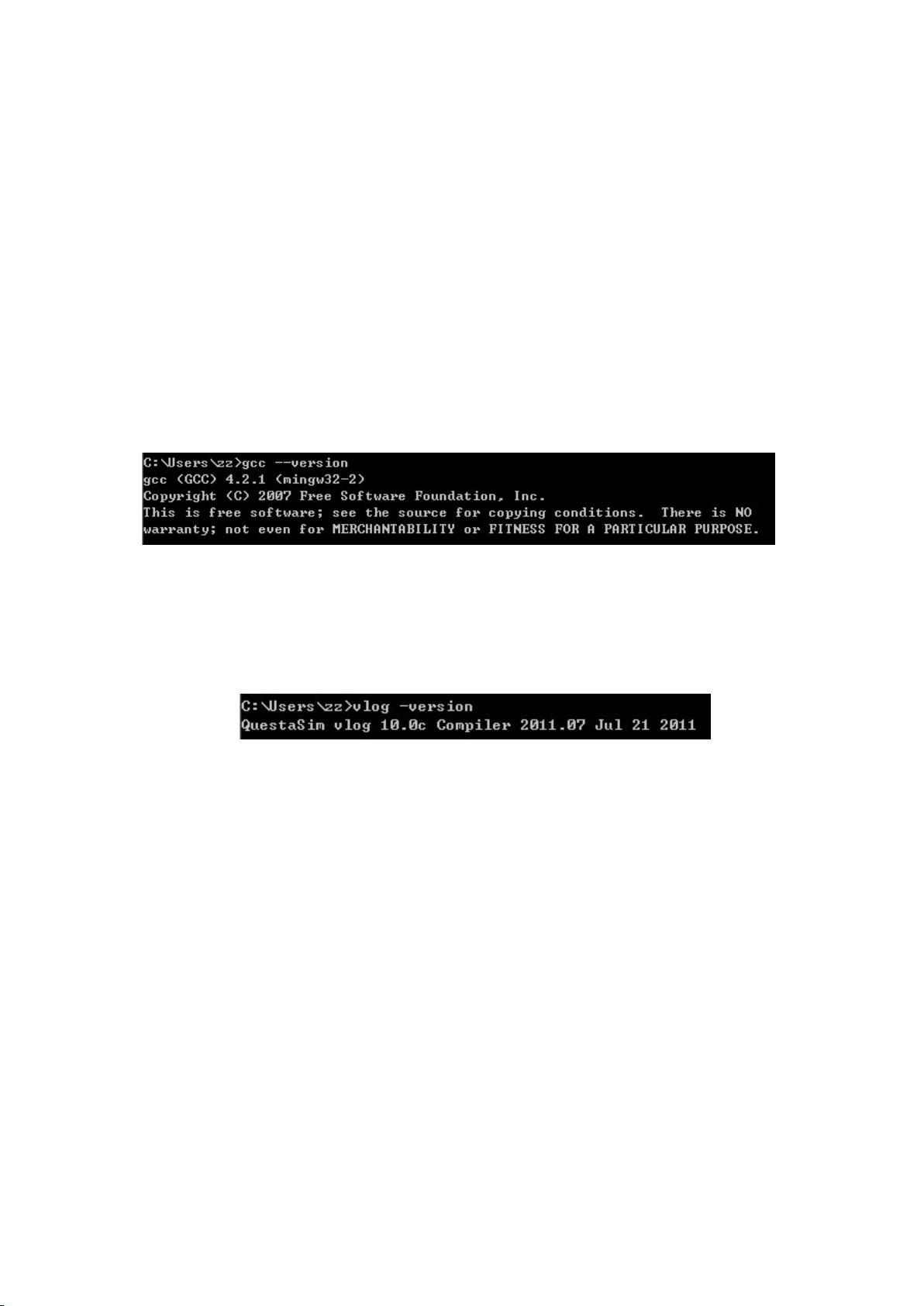

文档详细介绍了如何设置和配置UVM环境,如何编写和调试测试bench(测试向量生成器),以及如何理解和运用UVM的关键结构,如环境类(Env)、接口类(IF)、时序类(SeqItem)等。此外,作者还分享了他在使用QuestaSim时的学习经验,比如如何处理编译问题,如何理解和利用UVM的组件间协作。

在整个学习过程中,作者遇到的挑战包括中文资料的缺乏,这表明当时UVM在中国社区中的普及度不高。尽管如此,他还是通过网络搜索和专业论坛(如EETOP的IC验证板块)找到了必要的支持和解决方案。

总结来说,"UVM初级开发指南"是一篇实用的入门教程,不仅有助于读者掌握UVM的基本概念和实践,还能帮助他们理解如何在实际项目中运用这种验证框架,适合那些想要踏入验证领域的工程师或研究生。随着UVM在现代集成电路设计中的广泛应用,这篇文档的价值在今天依然不减。

2015-03-18 上传

2019-08-25 上传

2014-10-08 上传

2014-09-12 上传

点击了解资源详情

haohao

- 粉丝: 5

- 资源: 37

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器