数字逻辑课程设计:自动打铃器系统

需积分: 32 22 浏览量

更新于2024-09-12

2

收藏 4.12MB DOC 举报

"该资源是一份关于数字逻辑课程设计的报告,主要介绍了一个自动打铃器的实现。设计包括数字钟功能,能设置六个闹钟时间,并在设定时间响铃5秒。报告详细阐述了设计过程,各子模块的设计原理,如时钟信号发生模块、秒计数电路、分计数电路和小时计数电路。"

在这个自动打铃器的设计中,数字逻辑的概念被广泛应用。首先,设计者需要创建一个数字钟系统,它由几个关键模块组成,包括时钟信号发生模块、基本计时模块、动态显示模块、控制电路模块以及报时电路模块。这些模块协同工作,使得设备能够准确计时并按照预设时间提醒用户。

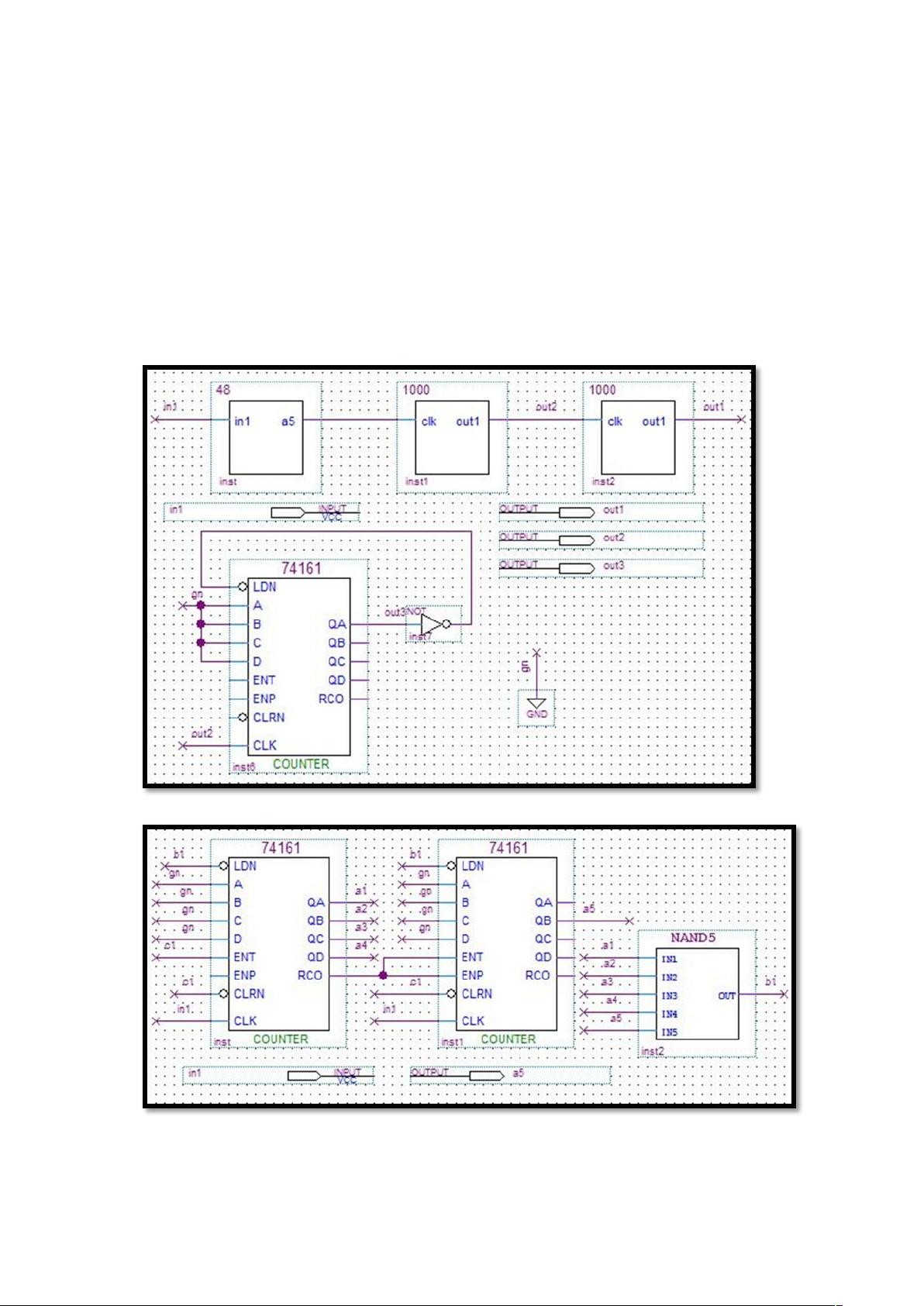

时钟信号发生模块是整个系统的基石,它需要生成不同频率的时钟信号,例如1Hz、100Hz、512Hz和1kHz。这通过将48MHz的系统时钟经过分频得到。48MHz的时钟信号先通过48进制和1000进制的计数器级联,产生所需的不同频率时钟。为了确保时钟信号的稳定,计数器采用了同步计数器设计,以避免逻辑冒险。

秒计数电路使用了两片74160模10计数器构成模60计数器,其时钟输入为1Hz的分频信号。当计数值达到59时,下一时刻的时钟信号会重置计数器为0。秒计数器的非门输出用于触发分计数器的进位脉冲,同时提供一个清零输入端,以在需要时初始化计数器。

分计数电路同样由两片74160构建,设计成模60计数器。除了计数到59时重置,还需要考虑秒计数器的信号,只有在秒计数为59时才允许下一次计数。这确保了小时、分钟和秒之间的同步。

小时计数电路使用了置数法设计,采用两片74160构成模24计数器。在秒和分计数都达到59的情况下,小时计数器才会更新,保持整体计时的正确性。

整个自动打铃器的闹钟功能通过一组16位数据比较器(由4个7485组成)实现,比较当前时间与预设的六个闹钟时间。当匹配到设定时间时,系统会给蜂鸣器发送信号,从而触发5秒钟的响铃提醒。

在设计过程中,使用了硬件描述语言(可能为VHDL或Verilog)进行逻辑设计,并通过仿真工具验证各个模块的正确性。通过这些仿真波形图,可以看到各计数器在时钟信号驱动下的工作状态,确认了设计的有效性。

这个自动打铃器项目不仅展示了数字逻辑的基本原理,还涵盖了数字电路设计、分频技术、计数器应用、数据比较以及硬件仿真等多个方面,是数字逻辑课程设计的一个典型实例。

点击了解资源详情

215 浏览量

545 浏览量

2021-10-11 上传

359 浏览量

299 浏览量

497 浏览量

oooodq

- 粉丝: 1

- 资源: 1