时序逻辑电路解析:从触发器到同步D触发器

版权申诉

23 浏览量

更新于2024-06-29

收藏 1.57MB PPTX 举报

"电工电子技术--时序逻辑电路.pptx"

时序逻辑电路是数字电路的一个重要组成部分,它具备记忆功能,能够根据输入信号改变并保持自身的状态。触发器作为时序逻辑电路的基础,是连接组合逻辑电路与时序逻辑电路的关键。触发器有两个主要特征:一是它能够维持两种稳定状态,分别代表逻辑0和1;二是能够通过不同的输入信号设置为0或1状态。

触发器有多种分类方式。根据电路结构,可以分为基本RS-FF(锁存器)、同步FF(电平触发)、主从FF(脉冲触发)、边沿FF(边沿触发)以及基于CMOS工艺的FF。按照逻辑功能,触发器可以是RS、JK、D、T或T'类型。根据存储数据的原理,又分为静态FF和动态FF。

在所有触发器中,基本RS触发器是最简单的。它可以由与非门或或非门构建。例如,与非门构成的基本RS-FF具有保持、置1、置0和不定四种状态,其状态取决于S和R输入信号。或非门构成的RS-FF则在S和R同时为1时会导致不确定状态。基本RS触发器常用于键盘输入和消除噪声,因为它们提供直接的置位和复位功能。

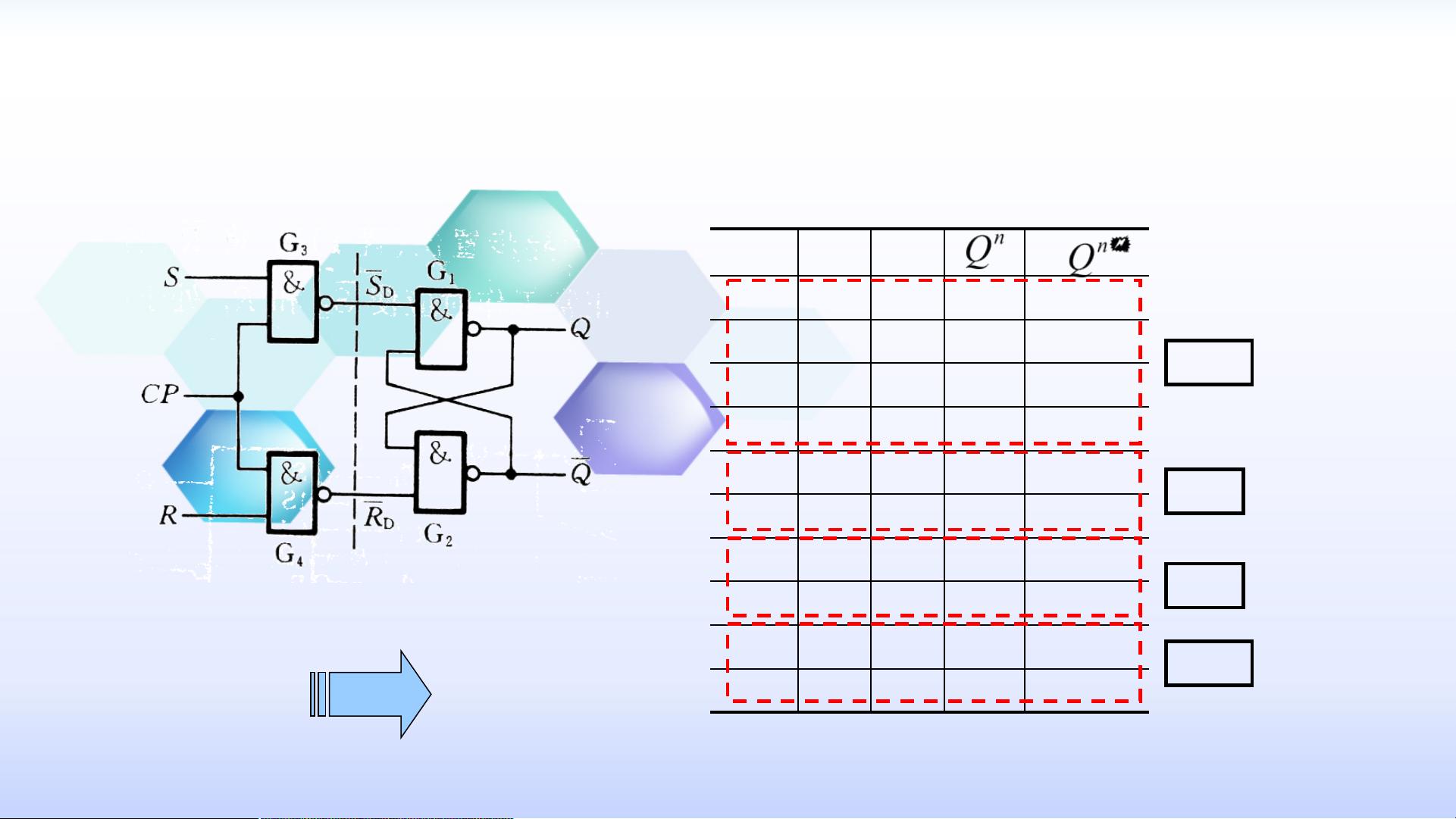

同步触发器,也称为钟控触发器,其状态的改变是由时钟脉冲(CP)控制的。在CP为高电平时,输入信号S和R的变化会影响触发器的输出状态。同步RS触发器在CP为1期间,如果输入信号S和R多次变化,会导致输出状态反复翻转,降低电路的稳定性。为解决这个问题,同步D触发器被引入,它只有一个数据输入D,并通过非门防止R和S同时为1的情况,从而避免了状态不确定性的问题。

同步D触发器的工作特点是,当CP上升沿到来时,D输入的状态会被无条件地装载到触发器的输出,即使在CP高电平期间D输入发生变化,输出也不会受到影响,这提高了电路的抗干扰能力。

时序逻辑电路通过触发器实现数据的存储和处理,同步触发器在数字系统中起到关键作用,特别是在需要精确时序控制的应用中。理解各种触发器的特性和工作原理对于设计和分析数字系统至关重要。

2021-10-06 上传

2021-10-06 上传

2021-10-12 上传

2021-10-12 上传

2021-10-04 上传

2022-10-30 上传

知识世界

- 粉丝: 375

- 资源: 1万+

最新资源

- rest-auth-proxy:基于Java的restful ldap-authentication微服务

- tkoopython:适用于Pythontkinter的面向对象的GUI演示的集合

- tApp:使用现代网络技术(HTML,CSS,JavaScript)构建tApp(TogaTech应用)的框架

- aabbtree-2.8.0-py2.py3-none-any.whl.zip

- acbm-predictor-senstivity-analysis:基于动物细胞的肉类(ACBM)成本预测模型的敏感性分析

- CI

- vetmanager-url-getter:通过诊所域名获取完整网址的简单包

- 西门子PLC写的超声波清洗机程序.rar

- Centric-Project:第12团队中心项目

- Python库 | django-mdeditor-widget-1.0.0.tar.gz

- Notes:使用美观的UI做笔记

- nutrition-calculator

- 行业分类-设备装置-一种造纸废水循环利用方法.zip

- tridium-eliwell-plc-webpage:Eliwell PLC的自定义网页

- gimli.units-feedstock:用于gimli.units的conda-smithy存储库

- btw-47.github.io