基于基于PCI总线的任意波形发生器的设计总线的任意波形发生器的设计

摘要:摘要:任意波形发生器是信号处理领域中必不可少的仪器设备,而很多任意波形发生器不能产生快速、有效、连续而且易于

定制的信号波形。本文提出了一种利用缓冲区快速交换数据、基于PCI总线的任意波形发生器的设计构想,依据该构想设计的

任意波形发生器可以快速进行数据更换,有效地保证了空间信号的连续性和多信号的快速切换。

关键词:关键词:PCI;任意波形发生器;连续

1 PCI总线介绍总线介绍

PCI总线是一种不依附于某个具体处理器的局部总线。从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,

具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。管理器提供了信号缓冲,使之能支持

10种外设,并在高时钟频率下保持高性能。

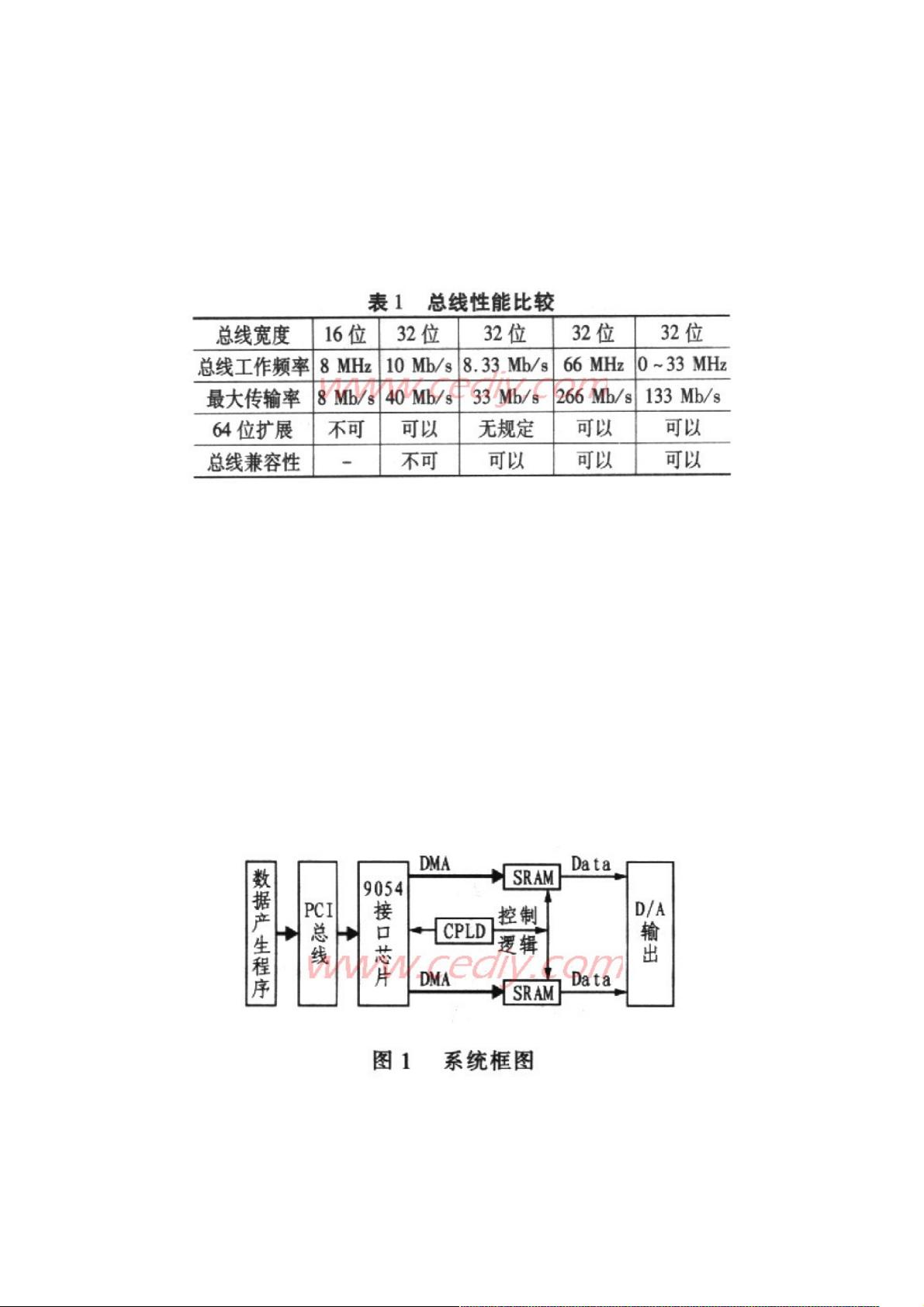

与其它总线相比,PCI总线标准具有多方面的优点。表1为几种总线性能的比较。PCI局部总线的性能特点如下:

(1)传输速度快。最高工作频率33 MHz,峰值吞吐率在32位时为132 Mb/s,64位时为264 Mb/s。

(2)支持无限猝发读写方式。读写时后面可跟无数个数据周期,具有强大的数据猝发传输能力。

(3)支持并行工作方式。PCI控制器具有多级缓冲,利用它可使PCI总线上外设与CPU并行工作。例如CPU输出数据时,先将

数据快速送到缓冲器中,当这些数据不断送往设备时,CPU就可转而执行其他工作了。

(4)独立于处理器。PCI在CPU和外设间插人一个复杂的管理层,用以协调数据传输,通常称之为桥。桥的主要功能是在两

种不同的信号环境之间进行转换,并向系统中所有的主控制器提供一致的总线接口。因此PCI总线可支持多种系列的处理器,

并为处理器升级创造了条件。

(5)提供4种规格,可定义32位/64位以及5 V/3.3 V电压信号。3.3 V电压信号环境的定义为PCI总线进入便携机领域提供了便

利。

(6)数据线和地址线采用了多路复用结构,减少了针脚数。一般而言.32位字长、仅作目标设备的接口只需47条引脚,作为

总线控制者的设备接口再加2条引脚,并可有选择地增加信号线扩展功能,如64位字长的接口卡需加39条引脚,资源锁定加l

条引脚,等等。

(7)支持即插即用功能,能实现自动配置。在PCI器件上包含有寄存器,上面带有配置所需的器件信息,使外设适配器在和系

统连接时能自动进行配置,无须人工干预。

2 设计流程设计流程

本设计的主要流程是将应用层程序产生的数据送入底层驱动,然后由底层驱动软件将数据分发到硬件的存储空间中。这一

过程由软件和硬件两部分完成。系统框图如图l所示。

2.1 软件设计软件设计

在本设计中,先通过高端数据处理软件进行信号的仿真处理,然后将仿真数据直接放入应用层缓冲区。由于本系统考虑到

适应一定的快速数据交换,理想状况下不允许出现空间信号的间断现象,因此在应用层开辟两块数据缓冲区,如图2所示,分

别标号BUFFERl和BUFFER2,在装完BUFFERl以后,再使用数据填充BUFFER2。只要软件设计的合理,就可以在应用层连

续地将交换数据。