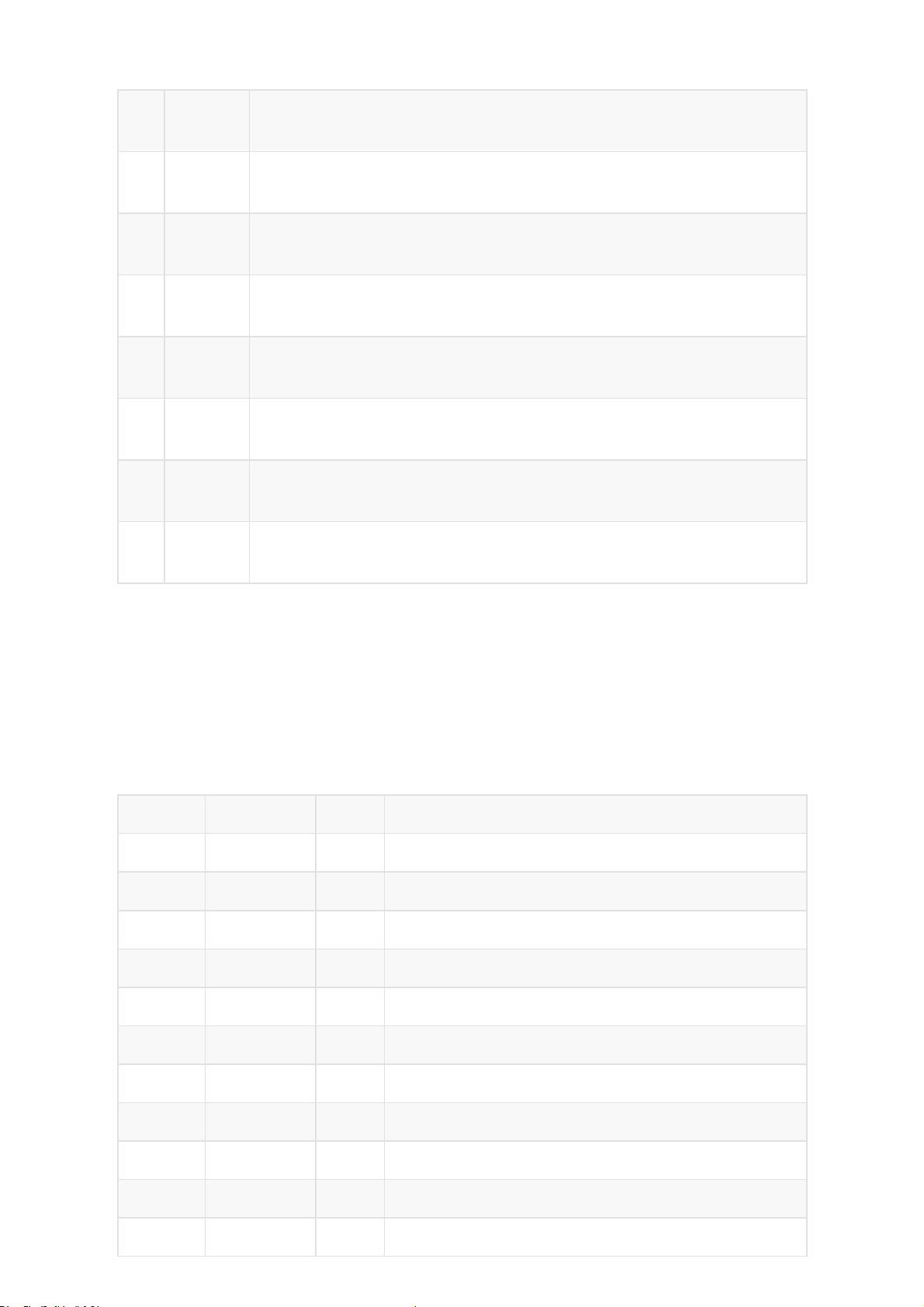

本微系统设计文档1介绍了D级和E级间的流水线寄存器,同时产生E级的控制信号。其中定义了端口输入/输出位宽,描述了下一个指令、RD1值、RD2值以及下一个PC的情况。此外,还详细介绍了nPCI32的设置下一个PC值的端口输入/输出位宽,并且说明了WEI1使能端、clkI1时钟信号和resetI1同步复位信号的作用。另外,还列出了不同功能的名称和描述,包括同步复位、取指令、取PC值和设置PC值等。

整体而言,该微系统设计方案为基于Verilog的MIPS微系统,包括流水线CPU、Bridge和计时器。CPU支持的指令集丰富多样,包括加载和存储指令(lb, lbu, lh, lhu, lw, sb, sh, sw)、算术指令(add, addu, sub, subu, mult, multu, div, divu)、逻辑指令(sll, srl, sra, sllv, srlv, srav, and, or, xor, nor)、立即数指令(addi, addiu, andi, ori, xori, lui)以及比较指令(slt, slti, sltiu, sltu)。该微系统设计文档详细介绍了每个部分的功能和设计方案,为MIPS微系统的实现提供了重要的参考。

微系统设计文档1对于MIPS微系统的D级和E级间的流水线寄存器、端口输入输出位宽以及不同功能的详细描述进行了全面的介绍,为开发人员提供了清晰而全面的设计指南。这些详细信息对于实际的MIPS微系统的实现具有重要的指导作用。同时,总体设计方案的概述也为整个微系统的开发提供了基本的框架和方向。通过本文档的综合阅读和理解,开发人员可以更好地了解MIPS微系统的设计、功能和实现细节,从而更加高效地进行系统开发和调试工作。

总之,微系统设计文档1提供了对MIPS微系统不同部分的详细设计方案,为开发人员提供了重要的参考信息。该文档的细致和全面性使其成为MIPS微系统开发工作中不可或缺的重要文献。通过对文档内容的仔细研读,开发人员可以更好地理解MIPS微系统的设计和实现细节,从而更好地进行系统开发和调试工作。