VHDL编程常见错误解析与对策

需积分: 35 201 浏览量

更新于2024-07-28

2

收藏 394KB DOC 举报

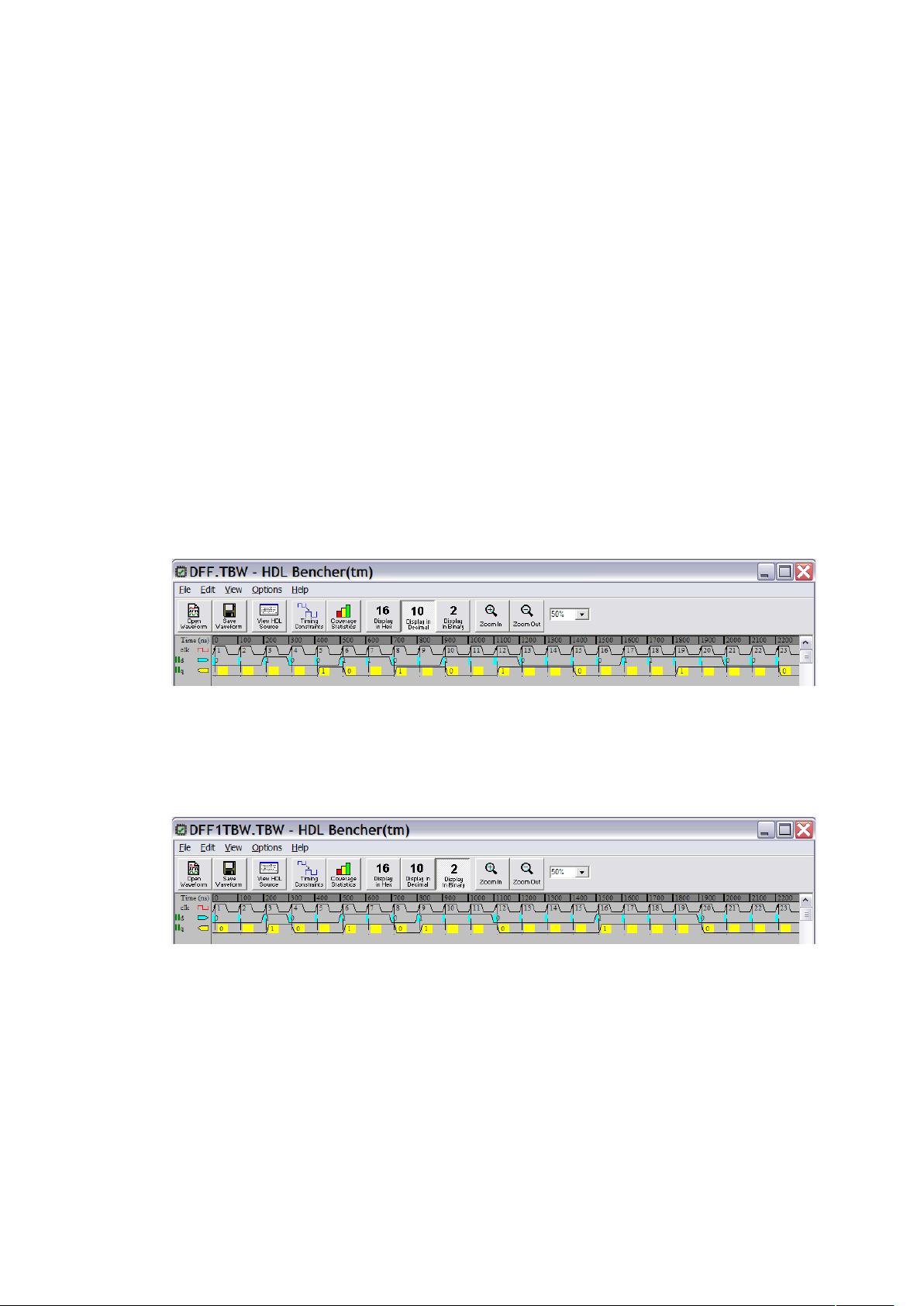

"VHDL常见错误及其原因分析,初学者在使用VHDL进行数字逻辑设计时可能会遇到的问题和解决方法,包括语法错误、信号与变量的理解与使用"

VHDL是一种硬件描述语言,用于设计和验证数字系统,如FPGA和ASIC。初学者在学习VHDL时,经常会遇到一些常见的错误,这些错误可能涉及到语法错误、信号和变量的误用,以及设计意图与实际实现不符等问题。

5.5.1 避免语法错误

VHDL的语法严谨,错误通常体现在以下几个方面:

1. **端口定义**:端口定义应遵循特定格式,如`port(端口名:端口类型 端口宽度)`,例如`port(clk: in std_logic; ...)`。端口类型包括`in`、`out`、`inout`,端口宽度用`std_logic_vector`表示,如`hour: in std_logic_vector(3 downto 0)`。

2. **信号和变量定义**:信号用`SIGNAL`声明,变量用`VARIABLE`声明。例如,`signal a: std_logic;`是信号,`variable c0, c1: integer;`是变量。信号可以视为连接硬件的线,而变量则类似于内存,用于临时存储数据。

3. **CASE语句**:CASE语句用于根据某个表达式的不同值执行不同操作,例如`case segis when "0000" => q <= "0000001";`。注意每个WHEN后跟一个条件,最后的WHEN OTHERS处理所有未明确定义的情况。

初学者必须熟悉这些基本语法,确保正确使用标点符号,以避免因小错误导致的设计失败。

5.5.2 信号与变量的区别

信号和变量在VHDL中扮演着不同的角色:

- **信号(Signal)**:模拟硬件中的实际连接,它们的改变是异步的,且可能在多个进程间传播。信号变化不会立即反映在计算结果中,而是延迟到下一次进程的敏感列表事件触发时。

- **变量(Variable)**:用于进程内部的临时存储,其变化是同步的,只在当前进程内可见。变量的改变立即生效,不影响其他进程。

理解这两者的区别至关重要,不恰当的使用可能导致设计逻辑的混乱,比如将应该使用信号的地方误用了变量,可能导致预期行为无法实现。

在VHDL设计中,需要根据设计需求正确选择使用信号还是变量。对于需要异步通信或状态保存的元素,应使用信号;而对于需要快速更新并仅在本地使用的临时数据,则使用变量。

掌握VHDL的基本语法和概念是避免错误的关键。通过不断的实践和学习,理解并熟练应用信号与变量,可以有效提高设计的准确性和效率。遇到问题时,查阅文档、教程或寻求社区支持也是解决困难的有效途径。

2011-10-12 上传

2023-03-25 上传

2023-08-20 上传

2023-05-12 上传

2023-05-03 上传

2023-06-07 上传

2023-05-18 上传

songisgood

- 粉丝: 491

- 资源: 20

最新资源

- Postman安装与功能详解:适用于API测试与HTTP请求

- Dart打造简易Web服务器教程:simple-server-dart

- FFmpeg 4.4 快速搭建与环境变量配置教程

- 牛顿井在围棋中的应用:利用牛顿多项式求根技术

- SpringBoot结合MySQL实现MQTT消息持久化教程

- C语言实现水仙花数输出方法详解

- Avatar_Utils库1.0.10版本发布,Python开发者必备工具

- Python爬虫实现漫画榜单数据处理与可视化分析

- 解压缩教材程序文件的正确方法

- 快速搭建Spring Boot Web项目实战指南

- Avatar Utils 1.8.1 工具包的安装与使用指南

- GatewayWorker扩展包压缩文件的下载与使用指南

- 实现饮食目标的开源Visual Basic编码程序

- 打造个性化O'RLY动物封面生成器

- Avatar_Utils库打包文件安装与使用指南

- Python端口扫描工具的设计与实现要点解析