Vivado HLS UltraFast设计方法指南

下载需积分: 5 | PDF格式 | 1.81MB |

更新于2024-06-29

| 184 浏览量 | 举报

Vivado HLS (High-Level Synthesis) 工具,这是Xilinx公司提供的一个高级综合工具,用于将高级语言(如C、C++或SystemC)编写的算法转换为硬件描述语言(如Verilog或VHDL)的实现,从而加速FPGA设计流程。 UltraFast方法是Vivado HLS的一种设计策略,旨在提高设计效率和性能。

1. **高效设计方法的需求**

随着电子系统复杂性的增加,传统的方法已经无法满足快速开发和优化大规模FPGA设计的需求。UltraFast Vivado HLS方法指南提供了一种高效的设计流程,帮助工程师更有效地利用FPGA的资源,缩短设计时间,并确保设计的性能和功耗。

2. **设计进程**

设计进程通常包括了系统设计、壳层(Shell)开发、基于C语言的IP核开发以及系统集成。在Vivado HLS中,这涉及到将高层次的设计抽象转化为硬件实现,通过C/C++代码进行功能验证,以及应用各种优化技术来提升性能。

3. **系统设计**

系统设计阶段包括了系统分区和系统开发。系统分区是将整个系统划分为不同的模块,每个模块可以独立开发。系统开发则涉及选择合适的处理元素,例如处理器、DSP块等,以及定义接口和通信协议。

4. **Shell开发**

壳层开发是创建一个包含FPGA外围设备和接口的框架,它为IP核提供了运行环境。壳层设计包括定义和实现与外部世界交互的接口,如内存接口、PCIe连接等。

5. **基于C语言的IP开发**

在这个阶段,开发者用C/C++编写算法,Vivado HLS会将其转换为硬件描述语言。快速的C语言验证允许工程师在软件环境中快速检查代码的正确性。C语言对综合的支持使得设计人员能够利用高级语言的抽象,同时进行硬件级别的优化。硬件优化的C库可以帮助提高性能。

6. **最优化方法**

Vivado HLS提供了多种优化策略,包括循环展开、流水线、资源复用等,以提高硬件的执行速度和资源利用率。RTL验证确保了转换后的硬件描述语言代码符合预期的功能和性能。

7. **系统集成**

系统集成阶段将各个IP核组合到一起,形成完整的系统。初始系统集成是验证各个IP核的互操作性,而自动执行的系统集成工具则简化了这个过程。面向未来的设计考虑了可扩展性和维护性,确保设计能够适应未来的需求变化。

8. **资源和法律声明**

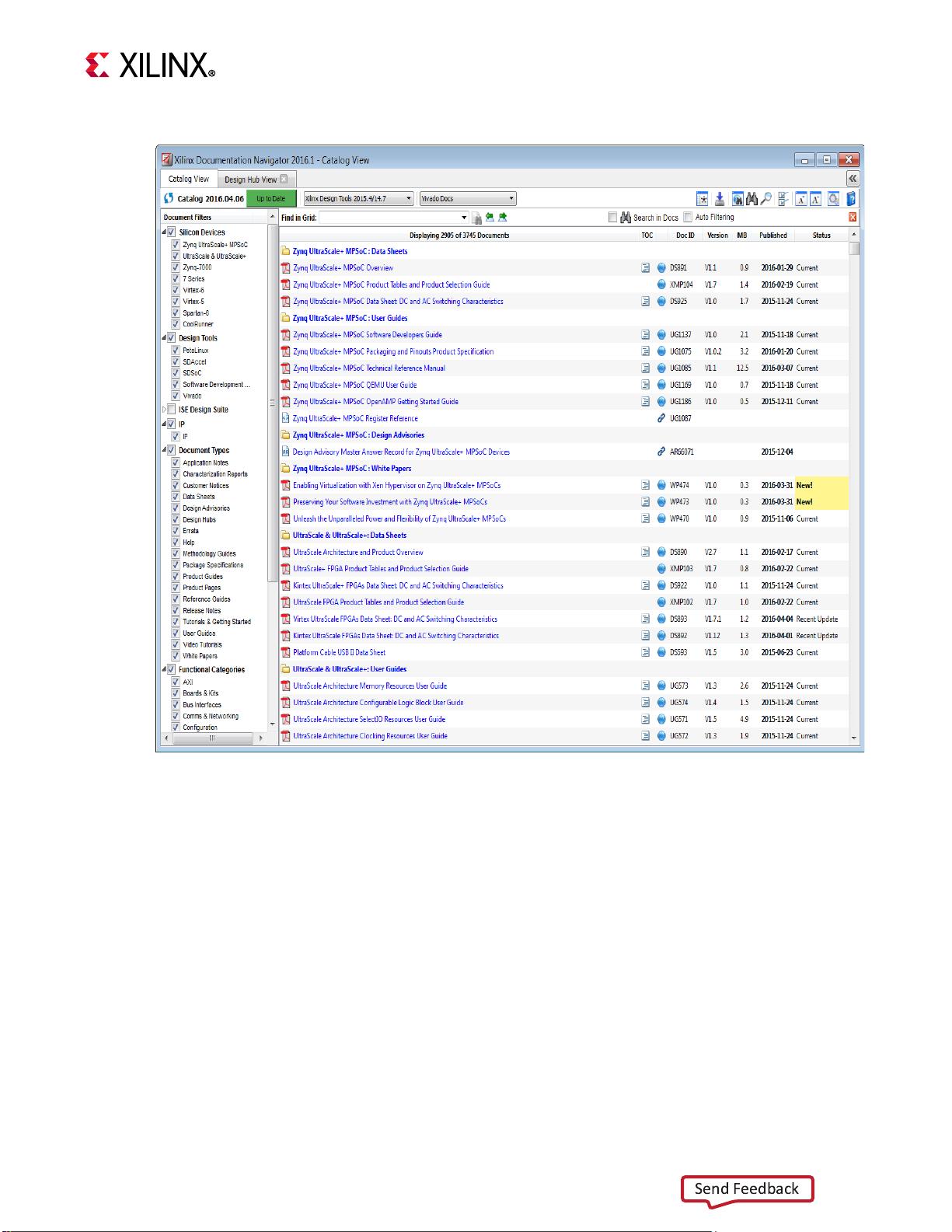

文档中还提到了额外的资源,如赛灵思解决方案中心、文献导航器和设计中心,这些都能为开发者提供进一步的帮助。同时,文档末尾包含了重要的法律提示,强调对知识产权和使用条款的尊重。

"UltraFast Vivado HLS方法指南"是FPGA设计者的重要参考资料,它提供了从高层次设计到硬件实现的全面指导,帮助用户在Vivado HLS环境下实现高效、高性能的FPGA设计。通过遵循这些最佳实践,设计者可以显著提高他们的设计生产力。

相关推荐

zaitax2011

- 粉丝: 0

最新资源

- 掌握JavaScript:经典实例全书源码解析

- VC++项目开发源代码精析:第一章至第四章

- 响应式FLAT商务宽屏Bootstrap项目源码下载

- TS文件解析:如何提取节目信息

- 专家推荐:PMP认证备考必备资料合集

- 虚幻引擎4构建RTS游戏的Agora项目介绍

- 绿色版jd-gui windows:Java反编译工具

- Apache Tomcat 7.0.65部署指南:跨平台Web服务器配置

- XiongFeiTan博客:Jekyll技术支持下的灵感与思考交流平台

- 绿色版驱动精灵单机版:简洁查看电脑设备

- ESP32-GUI-Flasher:全新GUI工具助力ESP32固件刷新

- SynToy:硬盘与U盘资源同步新工具

- 命令行工具wifi-password:跨平台获取wifi密码

- C# 双接口实现及定时器数据处理源码解析

- 细搜天气7.0.3黑莓免费版功能体验与更新问题

- Unreal Engine 4流映射燃烧效果Shader教程