使用Verilog设计与验证的双人赛跑计时秒表

"该资源是一份关于使用Verilog设计对两个运动员赛跑计时秒表的作业描述,包括秒表的功能、操作流程以及Verilog代码实现。"

在电子设计自动化(EDA)领域,Verilog是一种硬件描述语言,常用于描述数字系统的逻辑功能,如微处理器、接口控制器和定时器等。在这个特定的场景中,任务是设计一个能够计时并记录两个运动员赛跑时间的秒表。秒表的输入仅有时钟信号(clk)和一个按键(key),而key信号已经经过防抖动和脉冲宽度处理,每次按下key,它会在一个时钟周期内保持高电平。

秒表的操作流程如下:

1. 按下第一下key,秒表开始计数,并实时输出计数值。

2. 当第一个运动员到达终点时,按下第二下key,秒表记录第一个运动员的时间,但计数器仍在运行,持续输出计数值。

3. 当第二个运动员到达终点时,按下第三下key,秒表停止计数,此时的计数值代表第二个运动员的时间。

4. 随后,按下第四下key,秒表显示第一个运动员的计时,即第二次按键时保存的值。

5. 最后,按下第五下key,秒表清零,准备开始新的计时周期。

为了实现这个秒表,设计者采用了一种有限状态机(FSM)的方法。FSM通常由状态变量和转换条件组成,可以用来描述系统在不同条件下的行为。在这个设计中,FSM使用了ABC三位状态变量,通过卡诺图化简得到了次态方程,如A=BC, B=~BC+b~C, C=~A~C。每个状态对应秒表的不同操作,如开始计时(s_1)、持续计时(s_2)、暂停计时(s_3)、显示第一个运动员时间(s_4)和清零(s_0)。

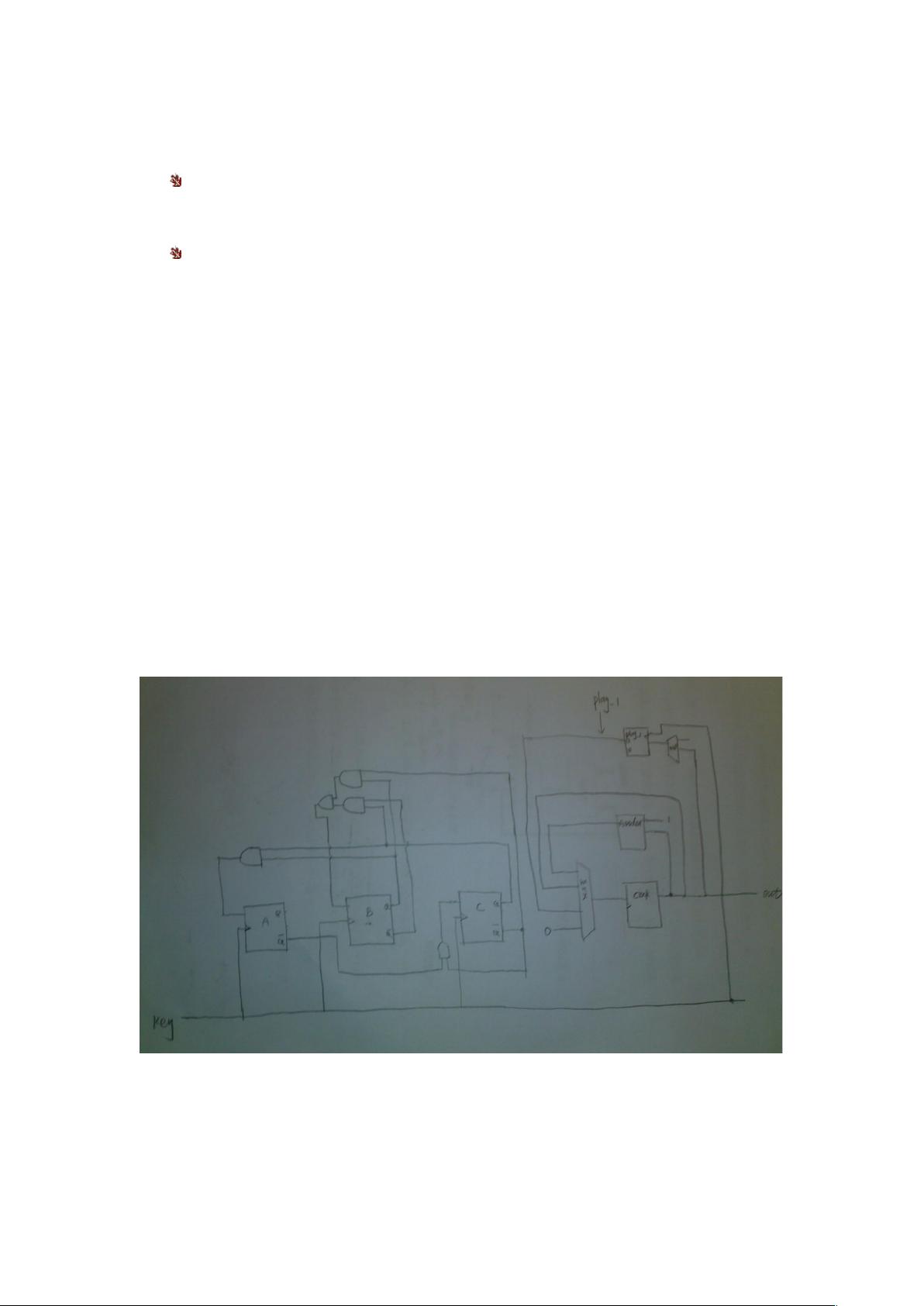

设计中使用了三个D触发器来存储状态变量,一个四选一多路选择器根据当前状态选择计数值输出(out),同时还有一个二选一多路选择器和D触发器来处理play_1信号,以确定是否显示暂停时的计数值。Verilog代码展示了如何在时钟边沿触发事件,例如,当key上升沿时更新状态机,以及在时钟上升沿时根据当前状态更新计数值。

代码中的关键部分包括:

1. `always @(posedge clk)` 语句表示在时钟上升沿触发的时序逻辑。

2. `case` 语句用于根据当前状态执行不同的计数操作。

3. `always @(posedge key)` 语句处理按键事件,更新状态机状态。

通过这种方式,Verilog代码实现了秒表的逻辑功能,并可以通过Cadence NC进行仿真验证,确保其正确性和可靠性。完成此设计后,设计者还需要绘制电路结构示意图,以可视化地展示各组件之间的连接关系。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2006-08-08 上传

2013-09-09 上传

2024-04-18 上传

2009-06-30 上传

2022-05-14 上传

2021-10-08 上传