MATLAB与FPGA联合仿真:极化码SCL译码器实现与性能优化

版权申诉

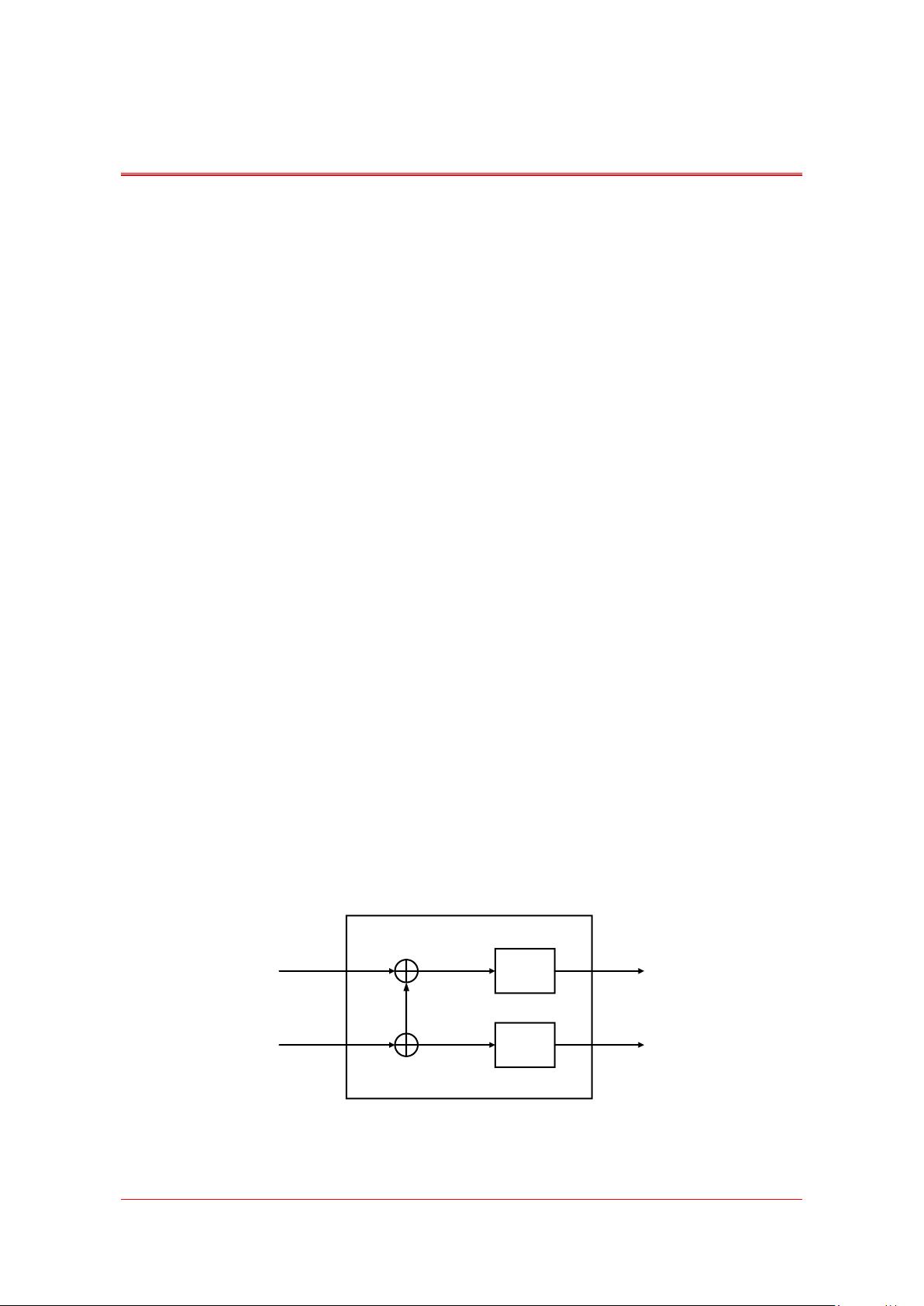

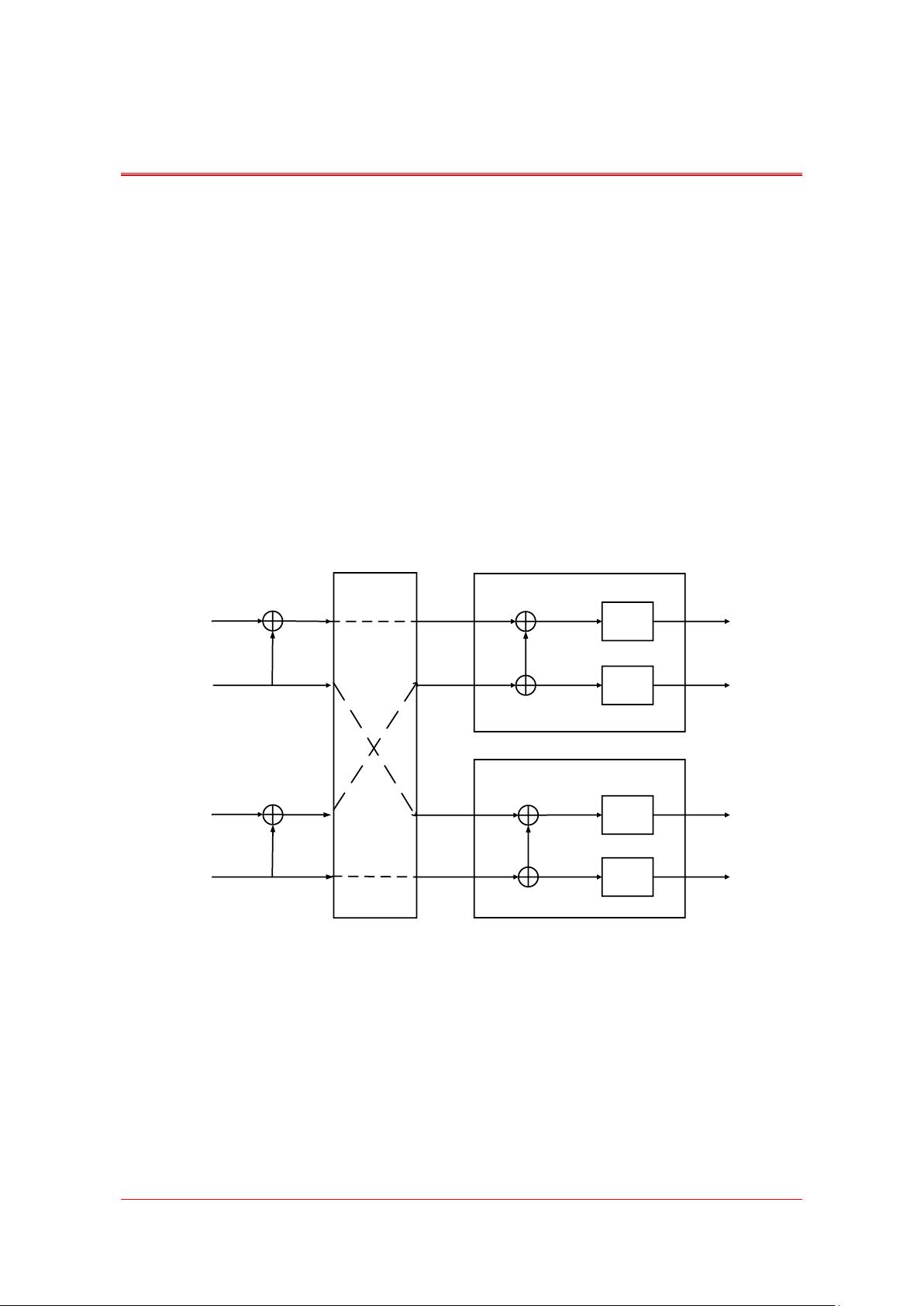

本篇论文主要探讨了极化码译码器的MATLAB与FPGA联合仿真方案设计与实现。极化码作为一种理论证明能够逼近信道容量的高效编码技术,在5G eMBB(增强移动宽带)应用中占据重要地位,特别是在控制信道编码中。论文首先对极化码的连续相消列表(SCL)译码算法进行了深入的MATLAB仿真分析,以理解其工作原理和性能。

接着,作者将SCL译码算法移植到FPGA平台上,通过AXI高级可扩展接口进行硬件实现。传统的MATLAB-FPGA联合仿真框架,即FPGA-in-the-Loop(FIL),虽然提供了基本的功能,但存在效率低下、硬件兼容性不佳的问题。为了解决这些问题,论文提出了两种改进的联合仿真方案:

1. 第一种方案基于网口连接,利用ARM在FPGA和MATLAB之间进行数据传输,并结合MATLAB与C语言的混合编程,以提高开发效率。这种方法通过网络协议实现MATLAB与FPGA间的实时通信。

2. 第二种方案则是基于PCIe连接,涉及FPGA端的逻辑设计、PC端的PCIe驱动程序以及C程序开发。C程序被编译成动态链接库,供MATLAB调用,实现了MATLAB与FPGA之间的高效交互。

在实际的Xilinx VC707和ZC706开发板上,作者进行了三种联合仿真方案的对比测试,结果显示,论文提出的两种新方案分别比MATLAB自带的FIL框架的仿真速率提高了70倍和166倍。当联合仿真帧数达到百万级时,这两种方案都能保持稳定运行,并且得到的仿真结果与理论预期高度一致。

本论文的核心贡献在于优化了极化码FPGA译码器的MATLAB联合仿真流程,提升了仿真效率和兼容性,为后续的极化码在实际通信系统中的应用提供了有力的工具支持。关键词包括极化码、连续相消列表译码、FPGA、联合仿真以及MATLAB的FIL框架。

1046 浏览量

2024-10-28 上传

137 浏览量

103 浏览量

2021-07-13 上传

272 浏览量

点击了解资源详情

xox_761617

- 粉丝: 31

最新资源

- Subclipse 1.8.2版:Eclipse IDE的Subversion插件下载

- Spring框架整合SpringMVC与Hibernate源码分享

- 掌握Excel编程与数据库连接的高级技巧

- Ubuntu实用脚本合集:提升系统管理效率

- RxJava封装OkHttp网络请求库的Android开发实践

- 《C语言精彩编程百例》:学习C语言必备的PDF书籍与源代码

- ASP MVC 3 实例:打造留言簿教程

- ENC28J60网络模块的spi接口编程及代码实现

- PHP实现搜索引擎技术详解

- 快速香草包装技术:速度更快的新突破

- Apk2Java V1.1: 全自动Android反编译及格式化工具

- Three.js基础与3D场景交互优化教程

- Windows7.0.29免安装Tomcat服务器快速部署指南

- NYPL表情符号机器人:基于Twitter的图像互动工具

- VB自动出题题库系统源码及多技术项目资源

- AndroidHttp网络开发工具包的使用与优势