华东理工Tomasulo算法实验:深入理解与操作详解

华东理工大学计算机体系结构实验二专注于Tomasulo算法的学习和实践,旨在通过深入理解指令级并行性和Tomasulo算法的工作原理,增强学生在设计和实现高性能处理器中的技能。实验分为三个主要部分,分别涉及指令流管理、浮点处理部件和保留站的结构。

首先,实验的主要目标包括:

1. 深入掌握指令级并行性的概念,了解如何在Tomasulo算法中利用并行计算来提高处理器性能。

2. 熟悉Tomasulo算法的具体步骤,包括指令的流入、执行和写回过程,尤其是对浮点指令和Load/Store指令的特殊处理。

3. 学习并理解浮点处理部件的结构,包括其内部操作的时钟周期延迟模型。

4. 掌握保留站的设计,这是Tomasulo算法的核心部分,用于暂存待操作的指令和数据,以便在不同阶段进行计算。

5. 实践能力的提升,即根据给定的代码片段,分析并预测每个时钟周期内保留站、指令状态表以及浮点寄存器状态表的状态变化。

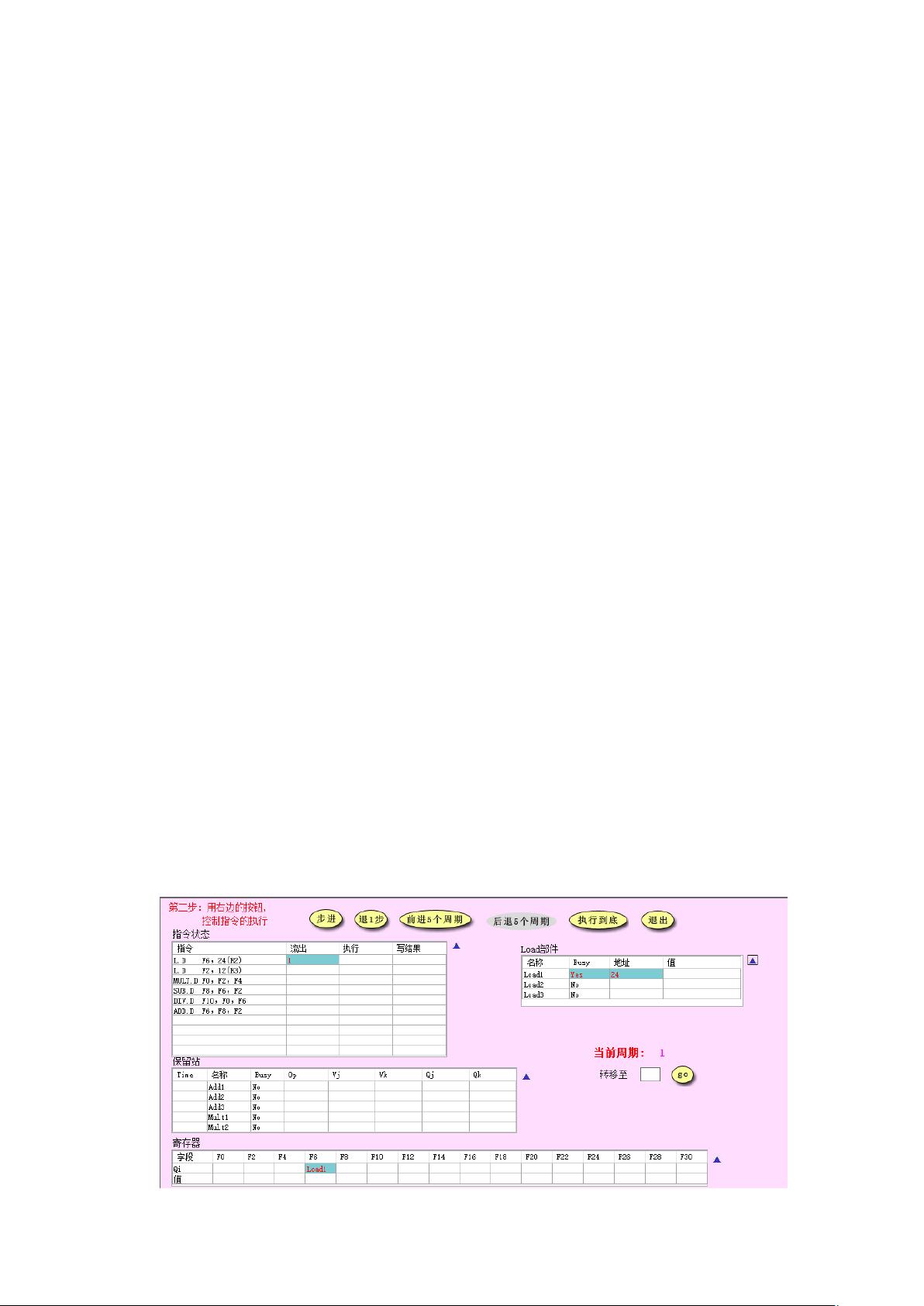

实验平台是基于Tomasulo算法的模拟器,让学生能够在虚拟环境中操作和观察算法的实际运行效果。

实验内容具体涉及到以下操作:

1. 对于一个包含浮点操作的代码段,例如加减乘除和Load/Store操作,要求学生在指令MUL.D即将写回时,准确描述保留站、Load缓冲器以及寄存器状态表中的内容。这需要对算法的执行顺序有清晰的理解,因为Tomasulo算法会在适当的时候分配运算资源,并确保数据的一致性。

2. 通过模拟器的步进执行模式,逐个时钟周期地跟踪指令的执行过程,观察指令状态表和寄存器状态表的变化,从而理解每个操作如何影响系统状态,以及如何通过保留站管理来实现指令的流水线处理。

在整个实验过程中,学生不仅要学习理论知识,还要具备将理论应用到实际问题解决的能力,这对于理解和优化现代计算机体系结构至关重要。通过这个实验,学生将深化对计算机体系结构的实践认识,为未来在相关领域工作打下坚实基础。

2023-03-10 上传

2023-05-30 上传

2023-09-16 上传

2023-03-27 上传

2023-06-08 上传

2023-06-12 上传

2023-02-22 上传

7_lining

- 粉丝: 29

- 资源: 9

最新资源

- 单片机串口通信仿真与代码实现详解

- LVGL GUI-Guider工具:设计并仿真LVGL界面

- Unity3D魔幻风格游戏UI界面与按钮图标素材详解

- MFC VC++实现串口温度数据显示源代码分析

- JEE培训项目:jee-todolist深度解析

- 74LS138译码器在单片机应用中的实现方法

- Android平台的动物象棋游戏应用开发

- C++系统测试项目:毕业设计与课程实践指南

- WZYAVPlayer:一个适用于iOS的视频播放控件

- ASP实现校园学生信息在线管理系统设计与实践

- 使用node-webkit和AngularJS打造跨平台桌面应用

- C#实现递归绘制圆形的探索

- C++语言项目开发:烟花效果动画实现

- 高效子网掩码计算器:网络工具中的必备应用

- 用Django构建个人博客网站的学习之旅

- SpringBoot微服务搭建与Spring Cloud实践