MTS锁存器与触发器:时序逻辑电路的关键组件

需积分: 5 14 浏览量

更新于2024-06-18

收藏 1.79MB PDF 举报

"11-12 锁存器和触发器.pdf"文档详细介绍了时序逻辑电路中的基本概念和两种关键逻辑单元——锁存器和触发器。这些知识点对于理解和设计现代电子系统至关重要。

时序逻辑电路

时序逻辑电路不同于组合逻辑电路,它不仅考虑当前输入信号,还会根据电路的原有状态进行操作。这类电路包含逻辑运算功能和存储单元(如锁存器或触发器),区分同步时序逻辑电路和异步时序逻辑电路,前者依赖于统一的时钟信号,后者则不受时钟控制,由输入信号的边沿触发变化。

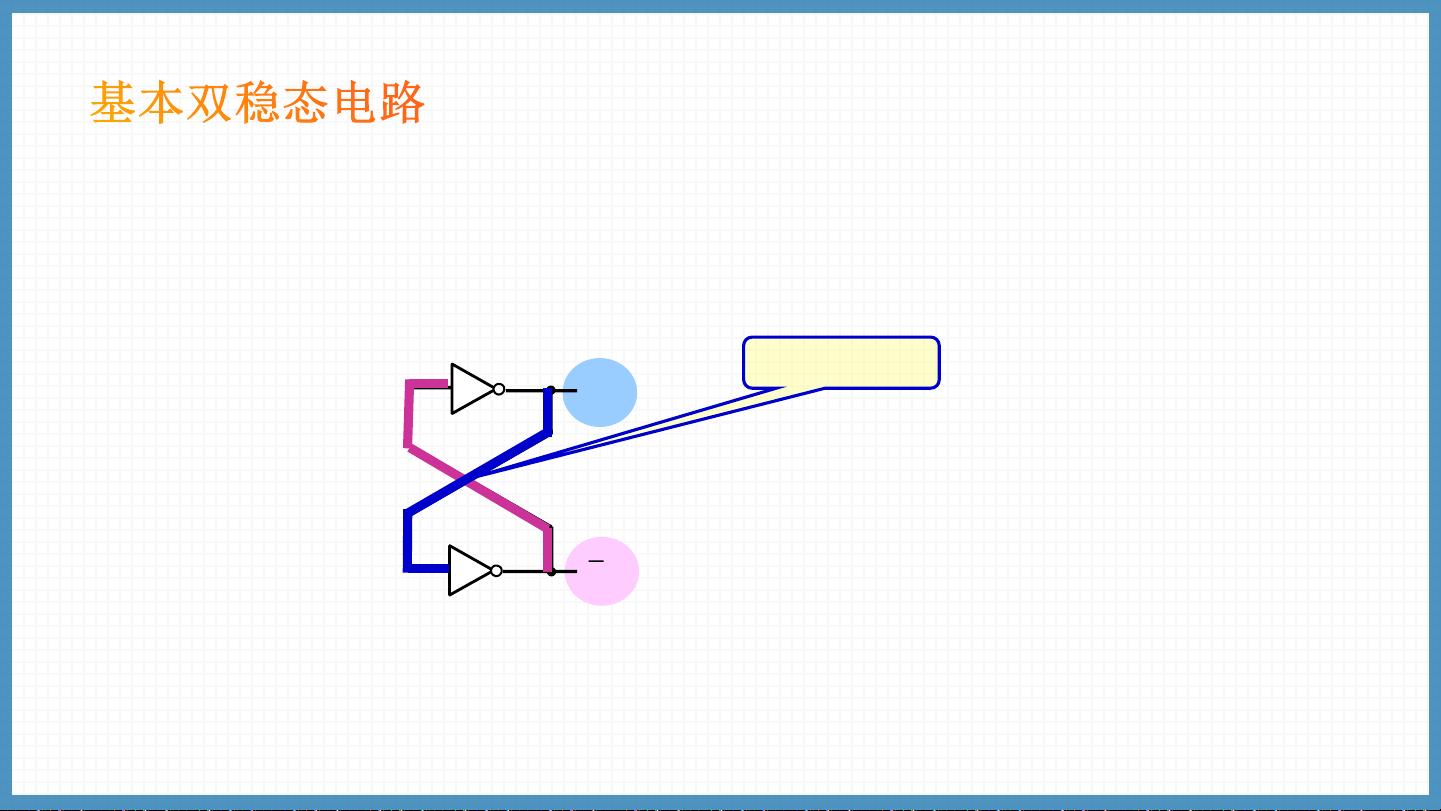

双稳态电路

双稳态电路的核心是具有两个稳定状态(通常为0和1)的电路,无论是锁存器还是触发器,都能存储一位二进制信息。锁存器对脉冲电平敏感,而触发器对脉冲边沿响应,如D触发器、JK触发器、SR触发器和T触发器等。

SR锁存器

SR锁存器,即Set-Reset Latch,通过两个输入(Set和Reset)来控制输出状态。其工作原理是,当Set为0且Reset为0时,状态保持不变;若Set置1或Reset置1,电路会进入另一状态。一旦电路状态被设定,即使信号消失,也会保持该状态直到下次信号变化。

文档强调了学习的重点,包括理解锁存器和触发器的工作原理,掌握它们的动态特性,以及如何应用不同类型的触发器(如SR、JK、D和T触发器)来实现特定的逻辑功能。此外,理解双稳态电路的结构,特别是如何通过基本电路设计实现数据存储和保持,是这部分内容的关键难点。

阅读和理解这份资料可以帮助读者深入掌握时序逻辑电路的基础理论,学会如何设计和利用锁存器和触发器构建复杂的逻辑系统,这对于电子工程领域的专业人士来说是一项必不可少的技能。

144 浏览量

198 浏览量

299 浏览量

2021-10-04 上传

2021-09-19 上传

185 浏览量

1615 浏览量

答案说明所有。

- 粉丝: 1w+

最新资源

- 久度免费文件代存系统 v1.0:全技术领域源码分享

- 深入解析caseyjpaul.github.io的HTML结构

- HTML5视频播放器的实现与应用

- SSD7练习9完整答案解析

- 迅捷PDF完美转PPT技术:深度识别PDF内容

- 批量截取子网页工具:Python源码分享与使用指南

- Kotlin4You: 探索设计模式与架构概念

- 古典风格茶园茶叶酿制企业网站模板

- 多功能轻量级jquery tab选项卡插件使用教程

- 实现快速增量更新的jar包解决方案

- RabbitMQ消息队列安装及应用实战教程

- 简化操作:一键脚本调用截图工具使用指南

- XSJ流量积算仪控制与数显功能介绍

- Android平台下的AES加密与解密技术应用研究

- Место-响应式单页网站的项目实践

- Android完整聊天客户端演示与实践