FPGA功耗优化:关键技术与设计策略

PDF格式 | 187KB |

更新于2024-08-30

| 55 浏览量 | 举报

随着科技发展和环保意识的增强,节能已经成为系统设计的重要考量因素,特别是在FPGA领域。FPGA(Field-Programmable Gate Array)因其灵活性和可重构性,为便携式系统提供了强大的潜力,但同时也带来了显著的功耗挑战。功耗问题不仅关系到产品的续航能力,也影响着设备的总体能源效率和环境影响。

在设计FPGA时,首先要理解功耗优化的重要性。一项最新调查显示,工程师们在设计优先级中将功耗置于前列,紧随性能、密度和成本之后。这意味着设计师必须在追求功能和速度的同时,找到降低能耗的有效途径。这涉及到深入研究FPGA的功率方程,这个方程反映了硬件结构、操作模式、时钟管理等多个方面的交互影响。

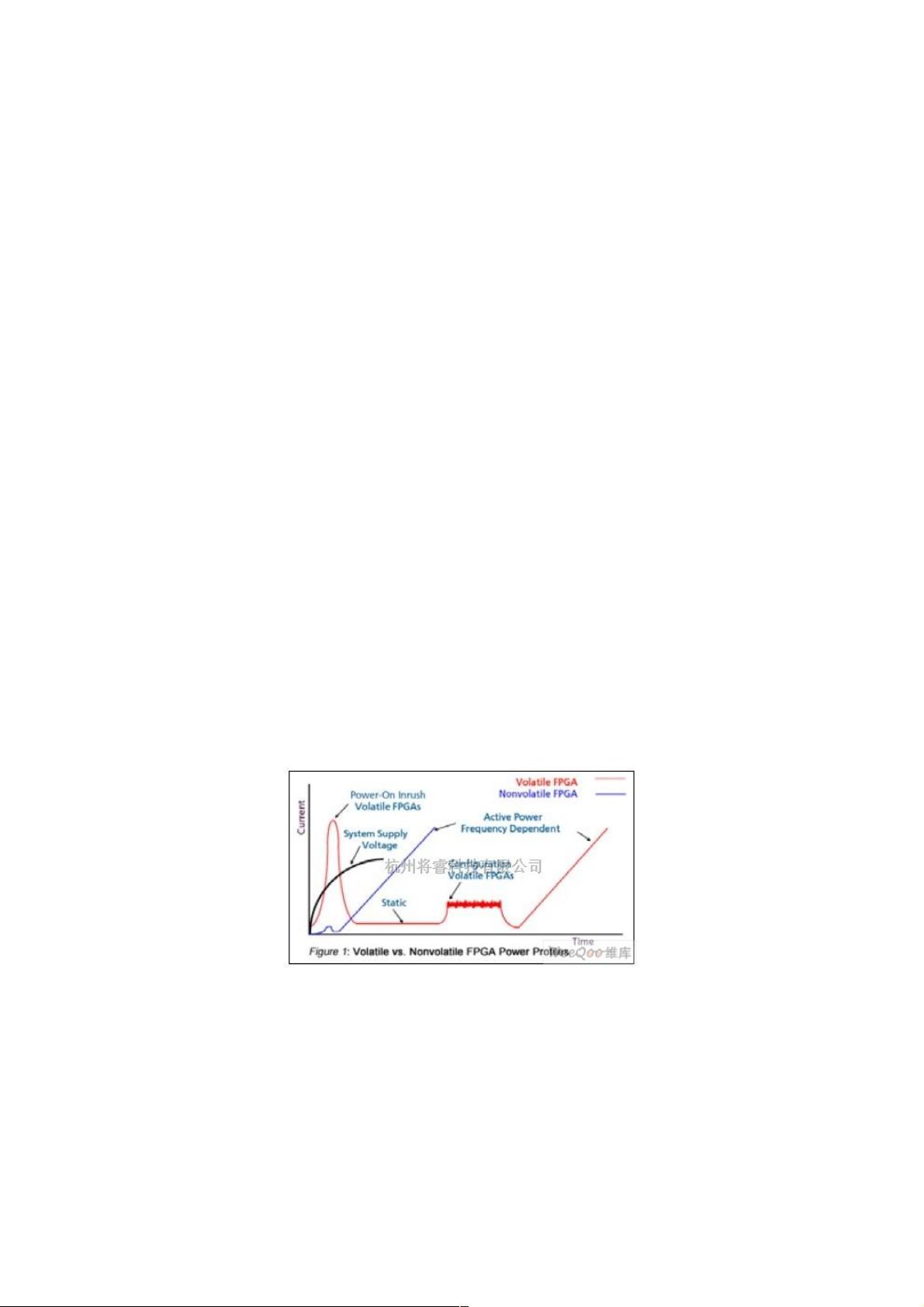

FPGA的功耗主要由静态电源、动态电源、上电/浪涌电源、配置电源以及不同低功耗模式等多种因素构成。静态电源,包括亚阈值泄漏、结泄漏、GIDL和栅极泄漏,即使在非工作状态下也会消耗能量。动态电源则随器件工作状态、资源使用情况、I/O负载、时钟频率等因素变化。设计易失性SRAM的FPGA时,还需考虑浪涌电源和配置电源,特别是系统启动阶段的瞬间供电需求。

为了优化FPGA功耗,系统设计人员需采取多种策略。首先,通过划分电路模块,合理分配任务可以降低整体功耗。其次,精细管理时钟,如使用异步时钟、锁相环路(PLL)优化或时钟门控,可以减少不必要的能源消耗。此外,电压分轨技术可以根据应用需求调整供电电压,进一步节省电力。还有,利用现代EDA工具,设计师可以进行详细的功耗分析和模拟,提前发现和解决潜在的功耗问题。

在具体实施过程中,设计师需要对每个FPGA技术类型的电源特性有深入理解,并结合实际应用场景选择最合适的低功耗模式。例如,对于移动设备,可能需要在运行核心任务时切换到低功耗模式,而在用户交互频繁时恢复高性能模式。

FPGA的功耗优化是一个多维度、技术密集型的过程,需要系统设计人员熟练掌握新型技术和工具,以实现高性能、低成本的同时,显著降低设备的能源消耗。随着FPGA在更多领域的应用,对低功耗设计的需求将持续推动EDA/PLD技术的发展,以满足绿色电子和可持续设计的要求。

相关推荐

weixin_38640443

- 粉丝: 10

- 资源: 885

最新资源

- jackson-core, Jackson的核心部分,它定义流API以及基本的共享抽象.zip

- MintyHydro:基于Arduino Raspberry Pi Zero W的Minty水培控制器

- 鼓风机和引风机的顺序功能.rar

- matlab代码sqrt-cnn_matlab:CNNMNIST从头开始分类

- 超高频RFID卡片检测demo

- pcb-canbus-to-spi

- spacer:穿越犹太城市的音频步道

- 深圳市合信MagicWorks HMI 3.6.1.zip

- Dism++系统设置小工具(禁用更新管理右键等).rar

- DataPipeline_wFlume:用水槽建立数据管道。 对于数据管道Pune聚会

- 弯管焊接机 摆动器(100行程).rar

- TrendCryptoCoin

- 基于Python的决策树判断是否降雪.zip

- jackson-annotations, 对于Jackson数据处理器,核心注解( 仅依赖于.zip

- rj-app:使用Nativescript设计的RJ事件的应用程序

- nodegrid-android-mdm