Verilog设计:交通灯实验与MAX II CPLD应用

需积分: 50 186 浏览量

更新于2024-09-13

11

收藏 2.77MB DOC 举报

在本实验中,学生针对具有倒计时显示功能的红黄绿三色交通灯设计进行自主选题实践,采用Verilog HDL(硬件描述语言)作为设计工具,这是因为Verilog以其强大的描述能力和灵活性,能精确地模拟和实现数字逻辑电路。Verilog被广泛应用于电子设计自动化领域,特别是在FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)的设计中。

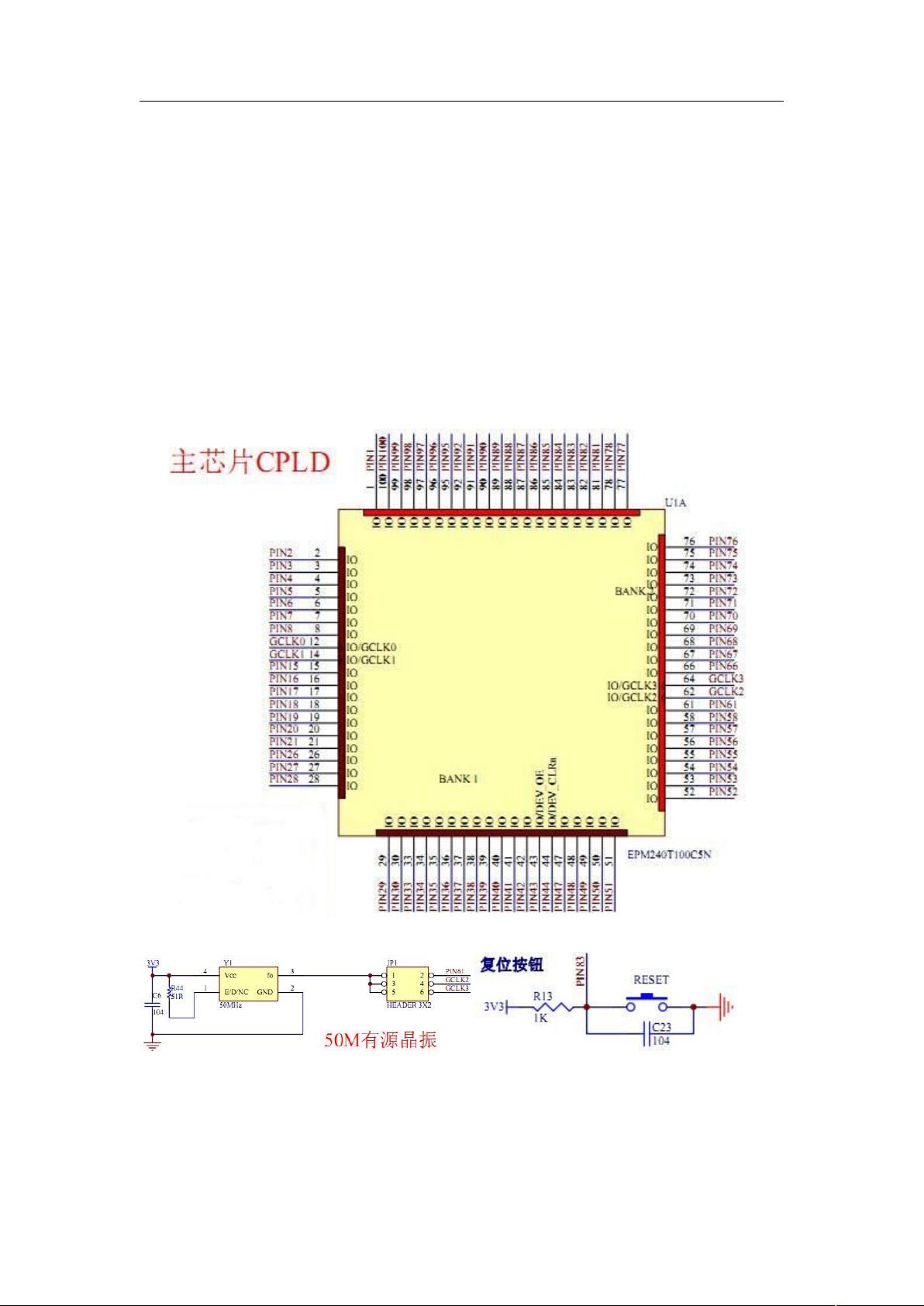

实验选择了Altera公司的MAX II EPM240T100C5作为主控芯片,MAX II系列是由Altera推出的一款性价比极高的CPLD产品。它具有创新的CPLD架构,提供了业界最低的成本和功耗,通过查表体系和TSMC的0.18um嵌入Flash工艺,实现了小型化。相较于上一代MAX系列,MAX II不仅价格降低了一半,功耗减少,而且保持了MAX系列的优点,如瞬态启动、单芯片设计和非易失性特性,同时性能提升明显。

实验的核心是交通灯设计流程,包括需求分析、功能模块设计、电路原理图绘制、Verilog代码编写以及实际电路搭建。在设计过程中,学生会深入了解交通灯的工作原理,如何根据红绿黄灯的切换规则来编程,以及如何利用MAX II器件的特性实现倒计时功能。此外,报告还会详细解释交通灯的逻辑结构,比如绿灯表示通行、黄灯作为过渡信号、红灯禁止通行,以及如何通过硬件设计确保信号的准确性和可靠性。

实验报告中不仅包含设计电路图,还会有实验代码示例,以便于其他学习者理解和复现。此外,为了验证设计的有效性,报告会附带实验结果的照片和测试数据,展示交通灯在实际运行中的工作状态和倒计时效果。

通过这个实验,学生不仅可以提升数字逻辑设计技能,锻炼实际操作和解决问题的能力,还能理解并应用现代硬件描述语言,增强理论知识与实践的结合。同时,由于交通灯设计与日常生活紧密相关,这个项目也有很强的实用性和教育意义。

4702 浏览量

1013 浏览量

103 浏览量

315 浏览量

162 浏览量

190 浏览量

zhouquan87

- 粉丝: 1

- 资源: 5