Xilinx MII to RMII接口设计与实现详解

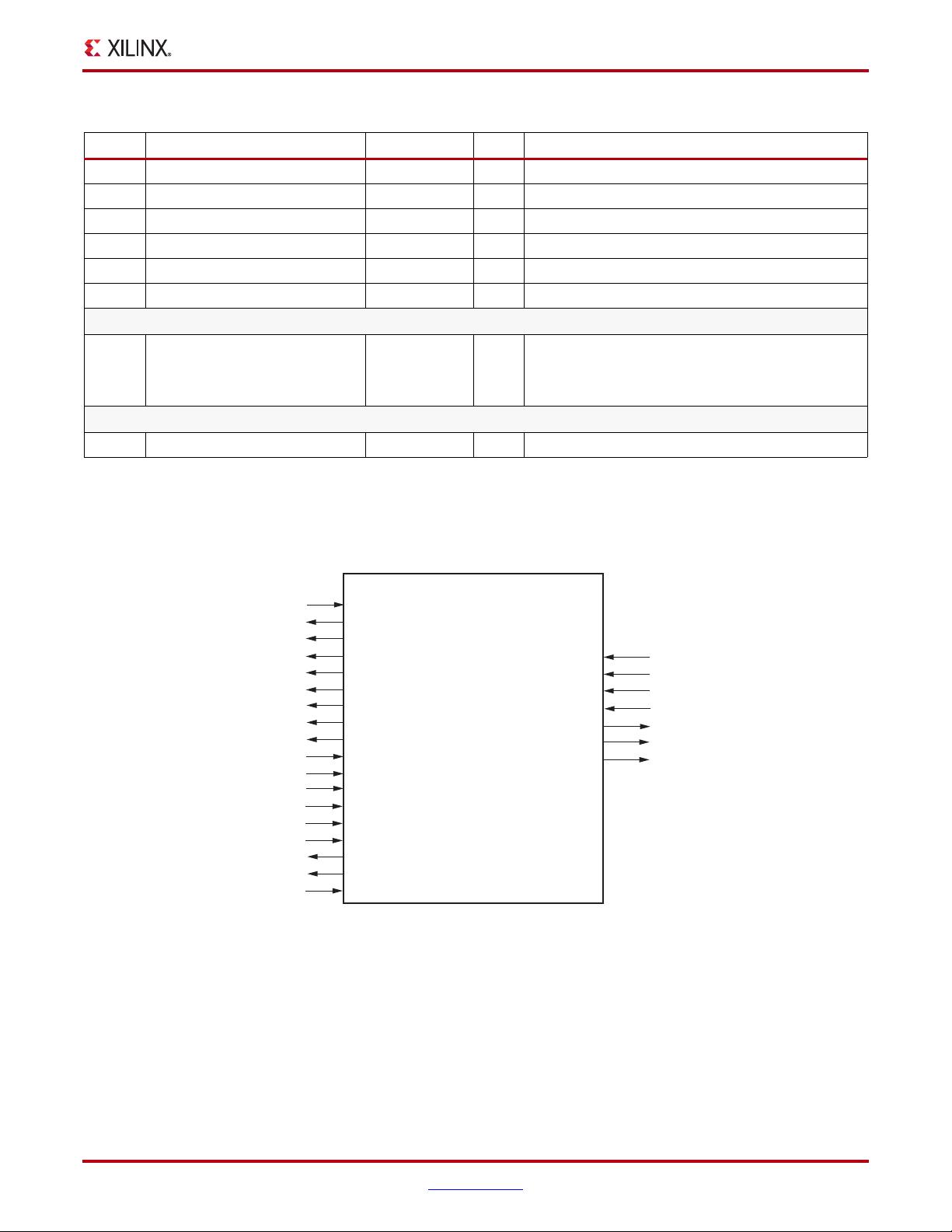

"MII2RMII接口是用于将遵循MII(Media Independent Interface)标准的以太网物理媒体设备(PHY)与Xilinx的10/100Mbps以太网核心,如XPS LLC TEMAC和XPSEthernet Lite进行连接的设计。MII接口通常需要16条信号线来与PHY通信,而RMII(Reduced Media Independent Interface)则通过减少信号数量(6或7条)来简化接口。MII2RMII IP核实现了这一转换,并通过一个固定的50MHz参考时钟同步两个接口,该时钟可以由外部源提供,也可以在主机FPGA内部生成。此核遵循RMII Consortium定义的版本1.0规范。"

本文档详细介绍了MII2RMII接口的实现方法,包括以下几个关键知识点:

1. **MII接口**:MII接口是一种通用的以太网接口,它定义了MAC层(Media Access Control)与PHY层之间的通信。MII接口有16条信号线,包括数据线、控制线和时钟线,用于在10/100Mbps速度下传输数据。

2. **RMII接口**:RMII接口是MII接口的一个简化版本,旨在减少所需的硬件资源。RMII使用6或7条信号线,通过半速率时钟来实现同样的功能,从而降低了成本和功耗。RMII接口适用于资源有限的嵌入式系统。

3. **MII2RMII转换**:MII2RMII IP核的主要任务是将MII接口的16条信号转换成RMII接口所需的较少信号,使得MII兼容的设备能够与RMII PHY进行有效通信。

4. **50MHz参考时钟**:MII2RMII核需要一个固定的50MHz参考时钟来同步两个接口的操作。这个时钟可以由外部提供,也可以在FPGA内部生成,确保数据传输的精确时序。

5. **Xilinx核心应用**:Xilinx的XPS LLC TEMAC和XPSEthernet Lite等核心采用传统的MII接口,而MII2RMII IP核使得这些核心能够与采用RMII的PHY器件协同工作。

6. **RMII Consortium规范**:MII2RMII IP核遵循RMII Consortium定义的版本1.0规范,确保与各种RMII-compliant设备的兼容性。

MII2RMII接口实现涉及到了网络通信中的物理层接口设计,特别是针对嵌入式系统的优化,以及FPGA中逻辑设计的灵活性。理解这些知识点对于设计和实现基于Xilinx FPGA的以太网解决方案至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-05-31 上传

点击了解资源详情

magicyang1986

- 粉丝: 0

- 资源: 2

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜