Verilog HDL语言入门教程

需积分: 13 110 浏览量

更新于2024-07-31

收藏 1.2MB PDF 举报

"这篇资料主要介绍了Verilog语言的基础知识,包括Verilog HDL语言的起源、发展历史,以及HDL的基本概念和仿真器的使用。资料来源于姜小波教授的《数字集成电路原理与设计》课程,适合学习数字集成电路设计的初学者。”

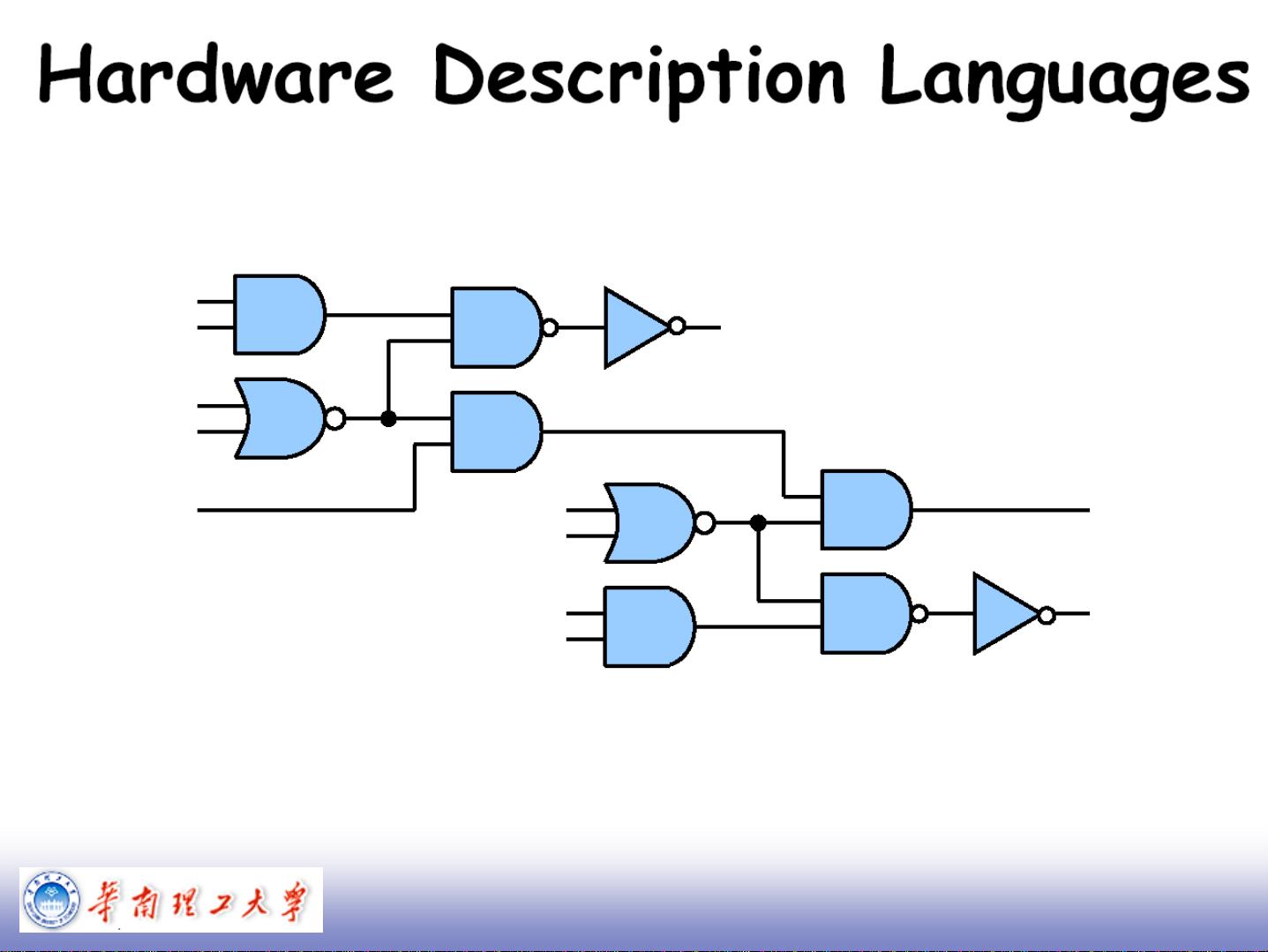

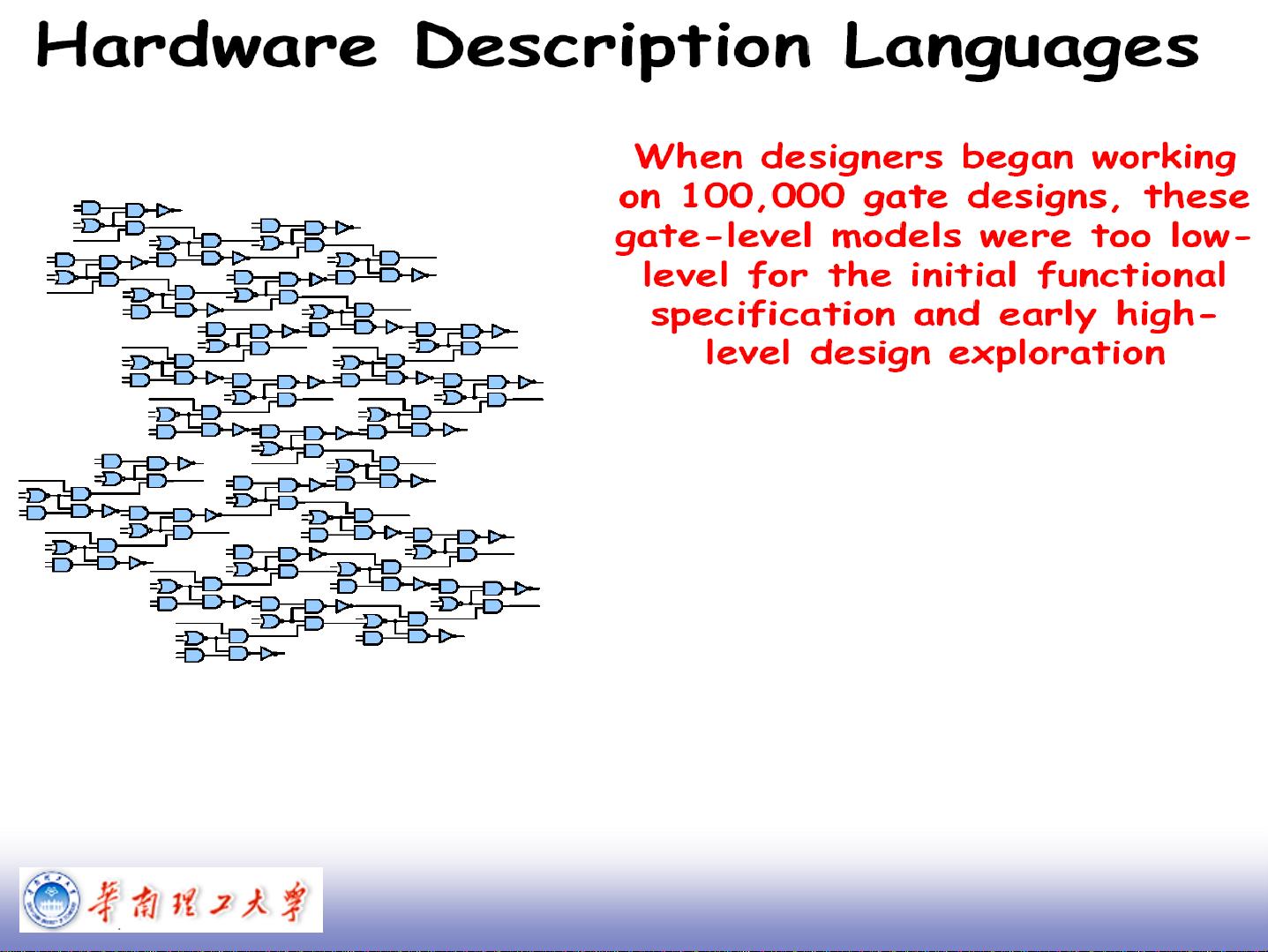

Verilog语言是电子设计自动化(EDA)领域中广泛使用的硬件描述语言(HDL),它允许工程师用类似于编程的语言来描述数字系统的结构和行为。Verilog HDL起源于1983年,由Gateway Design Automation公司发布,主要用于硬件设计的建模和仿真。1985年,Verilog仿真器进一步升级,被命名为Verilog-XL,提升了其在设计验证中的能力。

随着技术的发展,1987年Synopsys公司开始利用Verilog的行为级语言进行综合,这意味着Verilog不仅可以用于仿真,还可以参与到芯片设计的前端流程。1989年,Cadence公司收购了Gateway Design Automation,Verilog的影响力进一步扩大。1990年,Cadence成立了OpenVerilog International,推动Verilog语言的标准化和普及。

Verilog HDL语言分为结构级、行为级和混合级描述,可以用来描述数字逻辑的各种层次,从简单的逻辑门到复杂的ASIC(应用专用集成电路)设计。它的基本概念包括模块(Module)、实例化(Instantiation)、并行执行(Parallel Execution)、赋值操作(Assignments)、条件语句(Conditional Statements)、事件驱动(Event-Driven)、任务(Task)和函数(Function)等。

- **模块**:是Verilog中最基本的单元,可以代表一个逻辑电路,包含输入、输出和内部信号。

- **实例化**:允许将一个模块在设计中重复使用,类似于软件中的函数调用。

- **并行执行**:Verilog程序中的所有模块默认是并行执行的,反映了硬件并行处理的特点。

- **赋值操作**:包括连续赋值(Continuous Assignment)和阻塞赋值(Blocking Assignment)两种方式,分别用于描述静态逻辑和动态逻辑。

- **条件语句**:如`if-else`、`case`等,用于实现条件控制逻辑。

- **事件驱动**:基于时钟边沿或其他事件触发的操作。

- **任务与函数**:任务可以有返回值,可以在设计中异步执行;函数则没有返回值,同步执行,常用于计算。

在学习Verilog的过程中,除了理解这些基本概念,还需要掌握如何编写测试平台(Testbench)进行仿真验证,以及如何使用综合工具将Verilog代码转换为门级网表,最终实现硬件设计的目标。此外,了解和熟悉各种设计规范,如SystemVerilog扩展,可以提高代码的可读性和可重用性,对于现代复杂设计尤其重要。

Verilog语言的学习不仅是对语法的掌握,更是对数字系统设计思想的理解和实践。通过学习,工程师能够更高效地设计、验证和优化数字集成电路,为电子行业的创新和发展提供强大的工具支持。

点击了解资源详情

点击了解资源详情

点击了解资源详情

183 浏览量

1047 浏览量

1330 浏览量

618 浏览量

点击了解资源详情

点击了解资源详情

huagongxuexi

- 粉丝: 1

- 资源: 2

最新资源

- HTML5鼠标拖动游标滑块条显示百分比代码

- 移远EC20 R2.1.zip

- Too-Much-Munch

- fake-bpy-module:Fake Blender Python API模块集合以完成代码

- 基于Android平台智能门禁管理系统设计与实现.rar

- mybatisplus项目案例.zip

- matlab代码字的大小-CBIR:基于内容的图像检索系统

- Snippet-crx插件

- CSS3可爱害羞的小狗动画特效

- node-passport-login:一个Node.js项目,具有简单的注册和登录表单以及验证

- upptime-yandex-cloud:Yandex.Cloud的正常运行时间监控器

- app_ffmpeg_demo.7z

- 微信小程序canvas实现椭圆(圆形)元素自由移动

- tmux-mem:TPM的mem插件

- 截获WM_SIZING消息实现限制窗口大小]-易语言

- amazeui框架点击弹出头像上传代码