2. The stated maximum operating frequency must be observed when using the PLL with frequency modulation enabled.

Center-spread modulation is supported in cases where the nominal operating frequency plus half the modulation depth is

less than the stated maximum frequency.

3. Lifetime operation at Tj max not guaranteed. Standard automotive temperature profile assumed for performance and

reliability guarantees.

4. SVS guidelines apply to all LV supplies on the device. See power management chapter of device reference manual for

details on SVS.

5. The operating voltage range applies when the device is not in standby mode.

6. VDD_LV_PLL must be connected to VDD, and not powered independently. It must share any filters with VDD.

7. Both PCIe supplies must ramp for the SerDes PHY to safely power up into its reset state. Until both supplies are ramped,

the SerDes PHY will be in an undefined state.

8. A minimum of 2.91V is supported on this supply when the device is in low-power standby mode if it is kept powered during

this mode.

9. The device supports QSPI interface to 3.3V memories on the QSPI B bank, which is multiplexed with uSDHC functions on

the VDD_IO_SDHC supply. QSPI A signals on VDD_IO_QSPI are limited to 1.8V.

10. The VDD_EFUSE supply must be maintained within specification during fuse programming. Failure to do this may result in

improper functionality of the device after fuse programming.

11. Refer to the Power Sequencing section for the relationship of VDD_EFUSE powering up/down relative to the core,

high-voltage, and I/O supplies.

12. VDD_EFUSE must be grounded when not actively programming the fuses. This supply is not required to be powered for

fuse reads. See device hardware design guidelines document for more details.

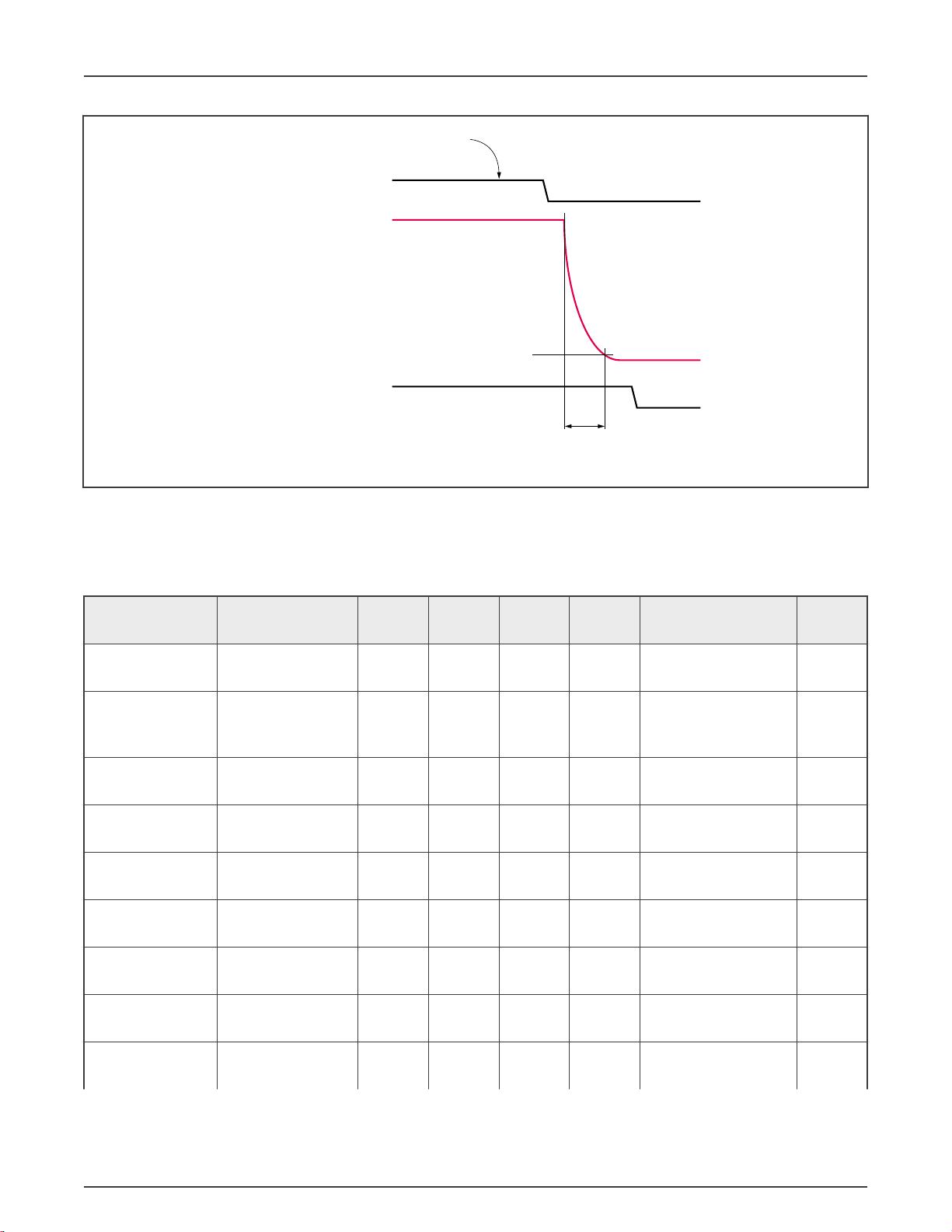

13. For AC signals, allowed max VIN ≤ VDD_IO* for lifetime operation. If AC overshoot beyond VDD_IO* occurs, then refer

to the Abs Max duration constraints as a function of the amount of overshoot. For DC signals ≥ VDD_IO, VIN-VDD_IO* ≤

0.3V is allowed for lifetime operation.

14. The min DC VIN level for a powered device is -0.3V. If AC undershoot below -0.3V occurs, then refer to the Abs Max

duration constraints as a function of the amount of undershoot.

15. DC case limit. Overshoot/Undershoot beyond this range is allowed, but only for the limited durations as constrained by

temporal percentages of tSIGNAL.

16. The "voltage differential" refers to the difference between the lowest and highest voltages across all supplies within the

supply group as defined under Condition column.

17. VREFH_ADCn allows a differential voltage of +/-100mV.

18. On slow ramps, the RESET_B pin may be observed to be asserted multiple times during the supply ramping. In order to

prevent these pulses from being propagated into the system, it is recommended that the PMIC drives RESET_B low during

supply ramp or whenever POR_B is asserted.

19. The maximum input voltage on an I/O pin tracks with the associated I/O supply maximum. For the injection current

condition on a pin, the voltage equals the supply plus the voltage drop across the internal ESD diode from I/O pin to

supply.

20. IINJ_D specifications are per pin for an unpowered condition of the associated supply. The maximum simultaneous

injection per supply is 30mA.

21. You must ensure that neither IINJ nor VIN specs are violated. Negligible DC injection currents are expected to flow during

normal powered operation.

22. The SAR ADC electrical specifications are not guaranteed during any period when the operating injection current limit is

violated. These specifications are at maximum Tj and VREFH_ADC=1.8V; the injected current will reduce with reduced Tj.

The “fuse setting” values/conditions in above table correspond with the DIE_PROCESS[1:0] fuses which NXP programs during

manufacturing. See Reference Manual and it’s Fuse Map for further details about the purpose. Example: Value “b01” represents

DIE_PROCESS[1]=0 and DIE_PROCESS[0]=1”.

The device hardware design guidelines document summarizes mandatory board design rules in table “Decoupling caps values”

and section “PDN (Power Delivery Network) Guidelines".

NXP Semiconductors

Operating Conditions

S32G2 Data Sheet, Rev. 6, 12/2022

Data Sheet: Technical Data 18 / 138