ADSP-BF537在视频SOC验证中的关键策略与嵌入式CPU选择

188 浏览量

更新于2024-08-31

1

收藏 535KB PDF 举报

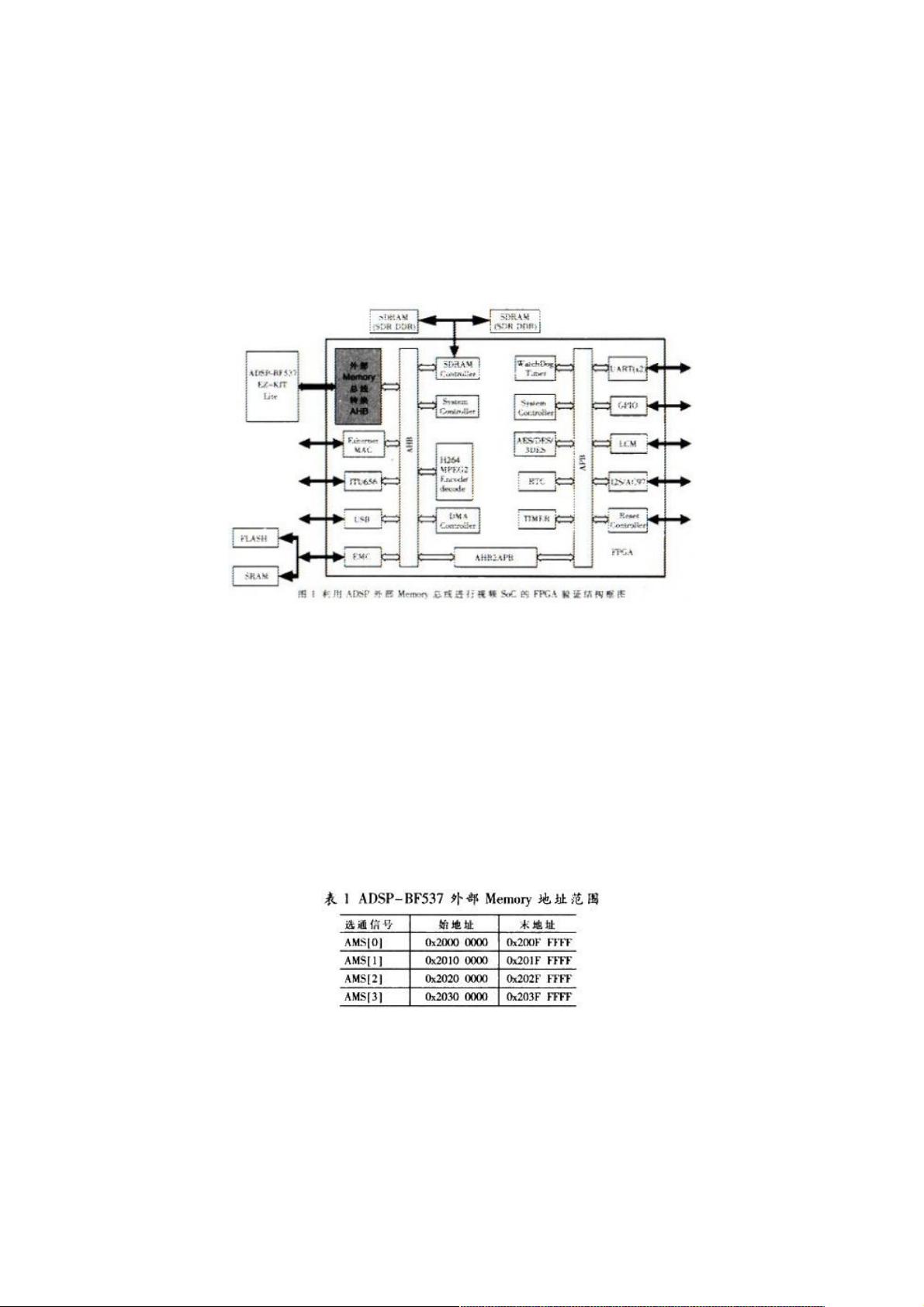

本文主要探讨了基于ADSP-BF537的视频系统-on-a-Chip (SoC) 验证方案,着重于在现代数字系统设计中的应用。随着集成技术的进步,SoC已经成为一种趋势,它将嵌入式CPU和存储器控制器集成在同一片硅片上,这带来了软硬件协同验证的挑战。

SoC的核心区别在于其集成的特性,包括内置的嵌入式CPU,如Blackfin处理器系列的ADSP-BF5xx,这些处理器以其高性能、低功耗和丰富的功能受到设计师青睐。文章提到的ADSP-BF533和后续的BF5xx系列,特别是BF537,以其16/32位RISC架构、10级流水线设计和内置的乘法加速器,成为视频SoC FPGA实时验证的理想选择。

外部内存总线设计也是关键环节,ADSP-BF537Ez-kitLite开发套件支持同步和异步操作,但地址空间有限,仅能访问19位地址。这种设计要求在选择SoC时充分考虑内存扩展和接口兼容性,确保软硬件之间的协同工作无缝进行。

此外,文章强调了基于IP的可重用设计方法在SoC设计中的重要性,设计者可以选择第三方提供的软核(源代码形式的处理器)或固核(已经实现的硬件设计),或者两者结合,以构建符合需求的系统。嵌入式CPU的选择不仅影响性能,还直接影响系统的整体效率和成本。

在实际的SoC验证过程中,软硬件协同测试必不可少,这涉及到CPU与外设、存储器以及外围设备之间的交互验证,确保整个系统在设计阶段就能满足实时性和可靠性要求。由于篇幅限制,文章并未深入探讨具体的验证流程和工具,但读者可以预期这会涉及硬件模型验证、软件模拟、硬件加速器验证等多个步骤。

本文提供了一个关于如何利用ADSP-BF537构建高性能视频SoC,并通过IP重用策略和软硬件协同验证来解决设计难题的方法论。这对于从事SoC设计、嵌入式系统开发和验证的工程师来说,是一份实用且具有指导意义的技术参考。

2023-03-05 上传

2023-03-05 上传

2011-11-24 上传

2020-10-19 上传

点击了解资源详情

2020-08-10 上传

2020-12-06 上传

2022-09-24 上传

2022-10-09 上传

weixin_38706531

- 粉丝: 3

- 资源: 945

最新资源

- lysmarine_gen:Lysmarine是基于raspbian操作系统的稳定性而构建的,可提供易于使用,稳定,低成本的船用导航计算机

- MWDM到底是什么?MWDM在5G商用中有什么样的作用-综合文档

- IGX:适用于Web和Facebook Instant Game开发人员的Facebook Instant Games包装

- js代码-js两个数对比对

- 机器学习动手:阅读和阅读Geron的第二版书

- Word Cookies For Pc [Windows And Mac]-crx插件

- pc端usb虚拟串口驱动

- ANTConnect-2021.39-py2.py3-none-any.whl.zip

- flowgallery_web:flowgallery.js的网站

- 新闻:使用现代Android开发构建的示例News:rolled-up_newspaper:应用[架构组件,协程,翻新,Room,Kotlin,Dagger]

- PM

- js代码-thirty seconds frequencies 发现数组中某一值出现的次数

- holbertonschool-low_level_programming

- 设计三极管放大电路有哪些技巧-综合文档

- vue3-clipboard:for Vue 3的剪贴板.js绑定

- imgrespo:typora图床仓库