SMT_PAAG处理器:硬件线程调度器提升69.25%性能

151 浏览量

更新于2024-09-01

收藏 261KB PDF 举报

"多核同时多线程处理器的线程调度器设计"

在当前的计算机硬件领域,多核处理器已经成为提升计算性能的关键技术。SMT_PAAG(Simultaneous Multithreading for Parallel and Array Graphic processors)处理器是专为图形、图像以及数字信号处理设计的多核处理器,它利用同时多线程技术,极大地提升了处理器的效能和资源利用率。本文将深入探讨其线程调度器的设计及其优势。

SMT技术允许处理器在同一时间处理多个线程,SMT_PAAG处理器可同时执行多达四个线程,这意味着在八个线程阻塞状态下,处理器仍能快速进行上下文切换,从而避免了由于线程等待而造成的性能损失。这种设计显著提高了处理器的工作效率,减少了空闲时间,使得处理器的资源得到了更有效的利用。

线程调度器是这一设计的核心部分,它负责决定哪些线程应当被赋予执行权。在传统的单线程或双线程处理器中,当一个线程因为等待I/O操作或内存访问等原因被阻塞时,整个处理器可能会进入空闲状态。然而,SMT_PAAG处理器的线程调度器能够在遇到阻塞的线程时,迅速切换到其他可执行的线程,保持处理器的持续运行,从而提高了整体系统性能。

在性能评测中,通过在SMT_PAAG处理器上运行图形处理算法,结果显示其性能提升了69.25%,这得益于处理器对指令级并行(ILP)和线程级并行(TLP)的深度挖掘。ILP是指在单个指令流中并行执行多个指令,而TLP则是在多个独立线程之间分配任务,两者结合使得处理器在面对复杂的并行任务时表现更佳。

并行计算的发展推动了处理器设计的创新。传统方法,如增加指令流水线宽度或提高时钟频率,受到应用程序的ILP限制和硬件复杂性、功耗等因素制约,无法持续提高处理器性能。因此,转向更高层次的TLP成为解决方案。像Intel的Hyper-thread技术、IBM的Power5、SUN的Niagara和中国的龙芯2号都采用类似的多线程技术来增强处理器的性能。

本文提出的线程调度器设计与Niagara处理器相比,拥有更大的核心数量和更多的线程支持。每个内核可以处理8个线程,总共16个核,允许同时执行的线程数达到64个。此外,它优化了线程切换速度,特别是在线程遭遇长周期指令时,能迅速切换到其他线程,避免资源浪费,进一步提升了处理器的效率。

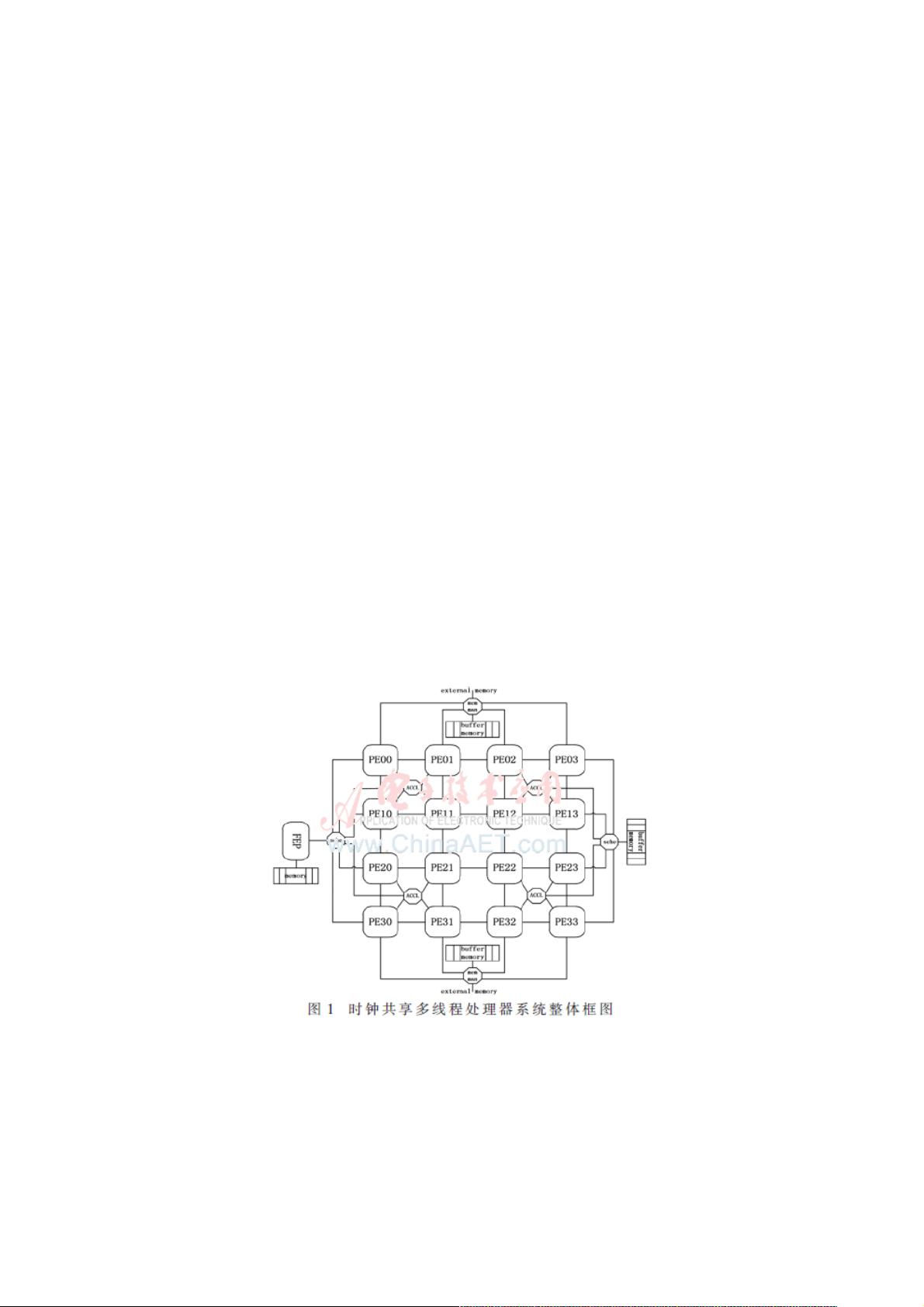

整体硬件结构方面,SMT_PAAG处理器采用时钟共享设计,支持MIMD模式,即每个核可以执行不同的指令流和数据流,允许并行执行多种任务。此外,处理器还具备分布式指令并行模式和流处理模式,以及异步执行、核间通信和线程间通信机制,这些特性使得处理器在应对各种工作负载时具有更高的灵活性和适应性。

SMT_PAAG处理器的线程调度器设计是提升处理器性能的关键,通过优化线程管理和上下文切换,不仅减少了等待时间,还有效地提高了资源利用率,为高性能计算和并行处理提供了强大的硬件支持。随着多核技术和并行计算的不断发展,这样的设计思路将继续推动处理器性能的不断提升。

2021-09-25 上传

论文

点击了解资源详情

论文

论文

点击了解资源详情

2023-07-08 上传

2023-05-24 上传

weixin_38645379

- 粉丝: 7

- 资源: 923

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦