Verilog实现FPGA奇偶校验原理与代码

版权申诉

200 浏览量

更新于2024-08-11

收藏 339KB PDF 举报

"该文档介绍了如何使用Verilog在FPGA上实现奇偶校验功能,包括奇偶校验的基本概念、输入数据的校验方法以及Verilog代码的编写。"

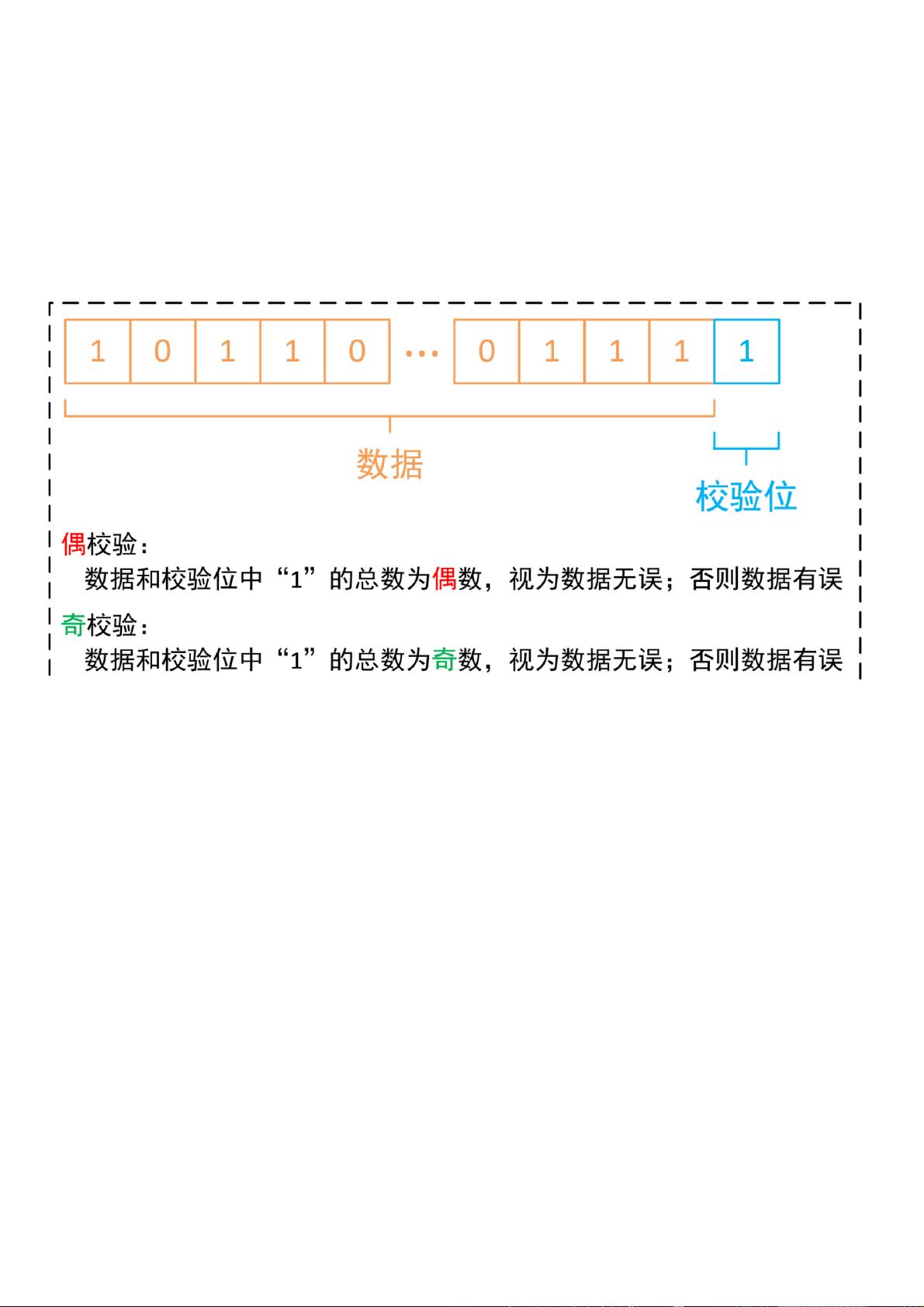

在电子工程领域,特别是在FPGA(Field-Programmable Gate Array)开发中,数据传输的准确性至关重要。奇偶校验是一种简单而有效的错误检测机制,用于确保数据在传输过程中没有发生错误。奇偶校验基于传输数据中的"1"的数量,分为奇校验和偶校验两种方式。如果数据中"1"的个数为奇数,那么奇校验位设为1,使得整个数据序列中"1"的总数为奇数;若数据中"1"的个数为偶数,则偶校验位设为0,保持总数为偶数。

例如,一个8位数据"11101000"包含4个"1"。采用奇校验时,会添加一个校验位1,使得总数据变为"111010001","1"的总数为5(奇数)。相反,若采用偶校验,校验位为0,总数据变为"111010000","1"的总数为4(偶数)。这样的校验可以在接收端检查,通过计算接收数据中的"1"数量是否与约定的校验类型匹配,来判断传输是否正确。

在实际应用中,数据通常是串行传输的,例如,数据"11101000"会以"0-0-0-1-0-1-1-1"的顺序逐位发送。对应的奇校验位"1-1-1-1-0-0-1-0-1"和偶校验位"0-0-0-0-1-1-0-1-0"会滞后一个时钟周期产生,便于与数据位拼接。

在Verilog中,可以使用时序逻辑来实现奇偶校验。例如,对于奇校验,初始设置校验位为高电平(1),每当检测到输入数据位为1时,校验位状态翻转。对于偶校验,校验位初始为低电平(0),同样在检测到输入位为1时翻转状态。以下是一个简单的Verilog模块示例:

```verilog

module odd_even1 (

input clk,

input in, // 串行输入

input reset, // 同步复位,高电平有效

output reg odd, // 奇校验位

output reg even // 偶校验位

);

always @(posedge clk) begin

if (reset) begin

odd <= 1'b1;

even <= 1'b0;

end

else begin

odd <= ~odd; // 奇校验实现

even <= ~even; // 偶校验实现

end

end

endmodule

```

这个模块在时钟的上升沿触发,如果处于复位状态,奇校验位设为1,偶校验位设为0。否则,根据输入数据的变化,奇校验位和偶校验位的状态将进行翻转,以此来实时生成校验位。

通过这种方式,开发者可以利用FPGA的硬件并行处理能力,在系统运行时快速准确地生成和检查奇偶校验,提高数据传输的可靠性。这对于需要高速、低延迟的数据通信系统,如通信接口、网络设备和存储系统等,具有重要意义。

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

2022-09-21 上传

_webkit

- 粉丝: 30

- 资源: 1万+

最新资源

- Haskell编写的C-Minus编译器针对TM架构实现

- 水电模拟工具HydroElectric开发使用Matlab

- Vue与antd结合的后台管理系统分模块打包技术解析

- 微信小游戏开发新框架:SFramework_LayaAir

- AFO算法与GA/PSO在多式联运路径优化中的应用研究

- MapleLeaflet:Ruby中构建Leaflet.js地图的简易工具

- FontForge安装包下载指南

- 个人博客系统开发:设计、安全与管理功能解析

- SmartWiki-AmazeUI风格:自定义Markdown Wiki系统

- USB虚拟串口驱动助力刻字机高效运行

- 加拿大早期种子投资通用条款清单详解

- SSM与Layui结合的汽车租赁系统

- 探索混沌与精英引导结合的鲸鱼优化算法

- Scala教程详解:代码实例与实践操作指南

- Rails 4.0+ 资产管道集成 Handlebars.js 实例解析

- Python实现Spark计算矩阵向量的余弦相似度