东南大学FPGA实验指南:组合与时序逻辑设计实战

需积分: 9 109 浏览量

更新于2024-07-24

收藏 1.03MB PDF 举报

本电子系统设计实验指导书针对FPGA技术展开,主要针对东南大学电子科学与工程学院的学生,旨在通过实践学习和理解FPGA的设计和应用。实验内容包括四个部分:

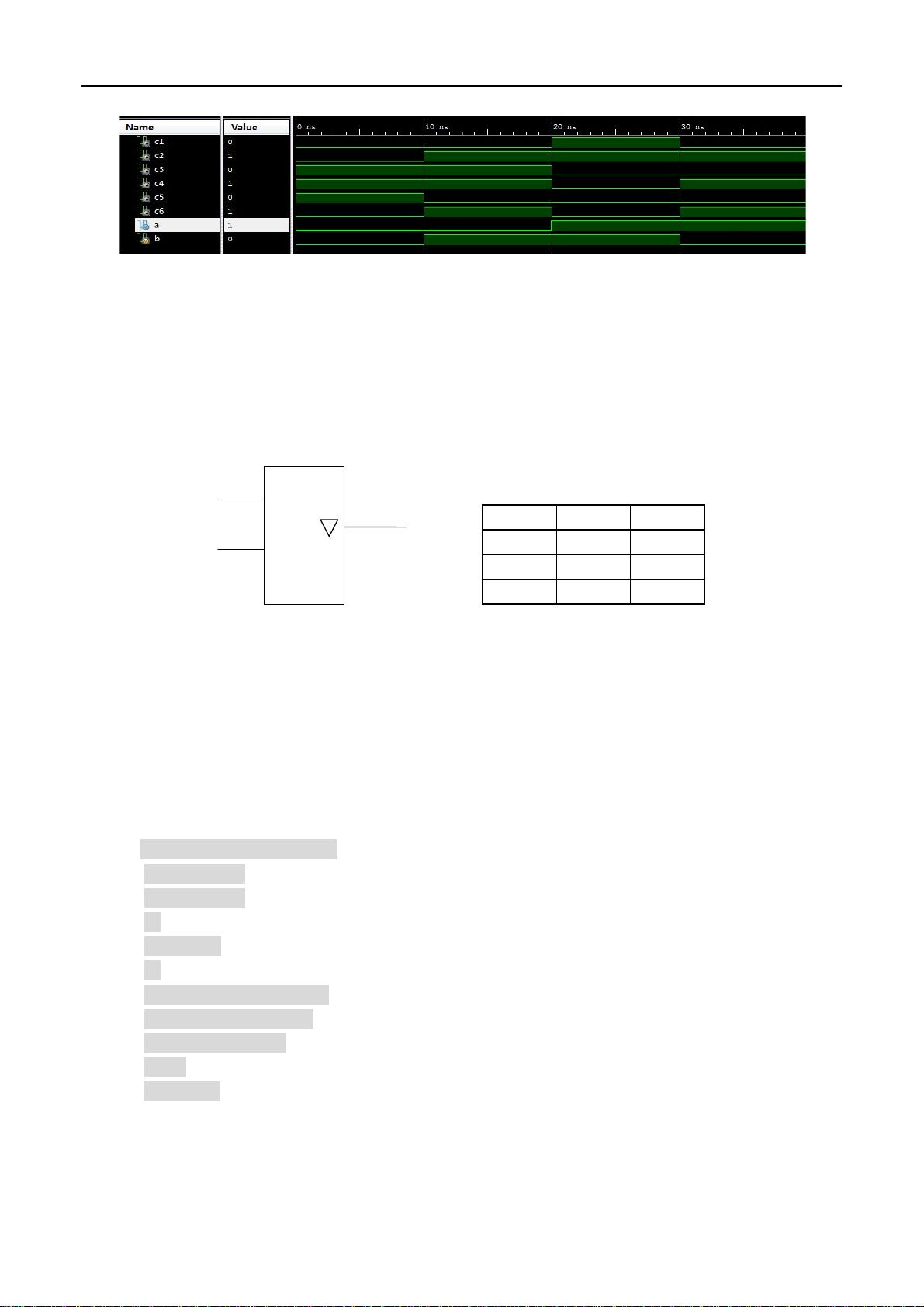

1. 组合逻辑电路设计(一):此部分让学生熟悉ISE 14.6编译环境,掌握Verilog HDL语言的基本编程流程,如输入源程序、编译、模拟仿真以及程序下载。学生需要实现简单门电路,如与非门、或非门等,并进行仿真和下载验证,以理解它们的工作原理和逻辑表达。

2. 组合逻辑电路设计(二):进一步深化对门电路的理解,可能涉及更复杂的逻辑结构,如三态门电路,同样要求通过编程和实际验证来增强理论知识。

3. 时序逻辑电路设计(一):进入时序逻辑领域,实验目标包括理解时序电路的设计原则,如触发器和计数器的实现,以及如何确保时序一致性。

4. 状态机设计:这一部分将理论应用于实际,通过构建状态机模型,使学生掌握状态转移和控制逻辑的实现,培养他们设计复杂系统的能力。

在整个实验过程中,强调了安全使用规范,如正确使用电源、保护电路免受静电干扰、注意液晶显示器件的操作、以及保持电路板整洁等,以确保实验过程的安全和实验结果的准确性。

通过这些实验,学生不仅可以提升FPGA设计技能,还能培养电路分析、逻辑设计和系统集成的能力,为后续深入研究和实际工程应用打下坚实基础。

2011-05-30 上传

2021-09-10 上传

2021-10-10 上传

2021-10-10 上传

2021-10-02 上传

2022-09-20 上传

2010-09-14 上传

2022-11-16 上传

u012732060

- 粉丝: 0

- 资源: 1

最新资源

- 达梦数据库DM8手册大全:安装、管理与优化指南

- Python Matplotlib库文件发布:适用于macOS的最新版本

- QPixmap小demo教程:图片处理功能实现

- YOLOv8与深度学习在玉米叶病识别中的应用笔记

- 扫码购物商城小程序源码设计与应用

- 划词小窗搜索插件:个性化搜索引擎与快速启动

- C#语言结合OpenVINO实现YOLO模型部署及同步推理

- AutoTorch最新包文件下载指南

- 小程序源码‘有调’功能实现与设计课程作品解析

- Redis 7.2.3离线安装包快速指南

- AutoTorch-0.0.2b版本安装教程与文件概述

- 蚁群算法在MATLAB上的实现与应用

- Quicker Connector: 浏览器自动化插件升级指南

- 京东白条小程序源码解析与实践

- JAVA公交搜索系统:前端到后端的完整解决方案

- C语言实现50行代码爱心电子相册教程