FPGA设计全程指南:多工具协同实战8-bit RISC CPU

需积分: 10 81 浏览量

更新于2024-08-06

收藏 750KB PDF 举报

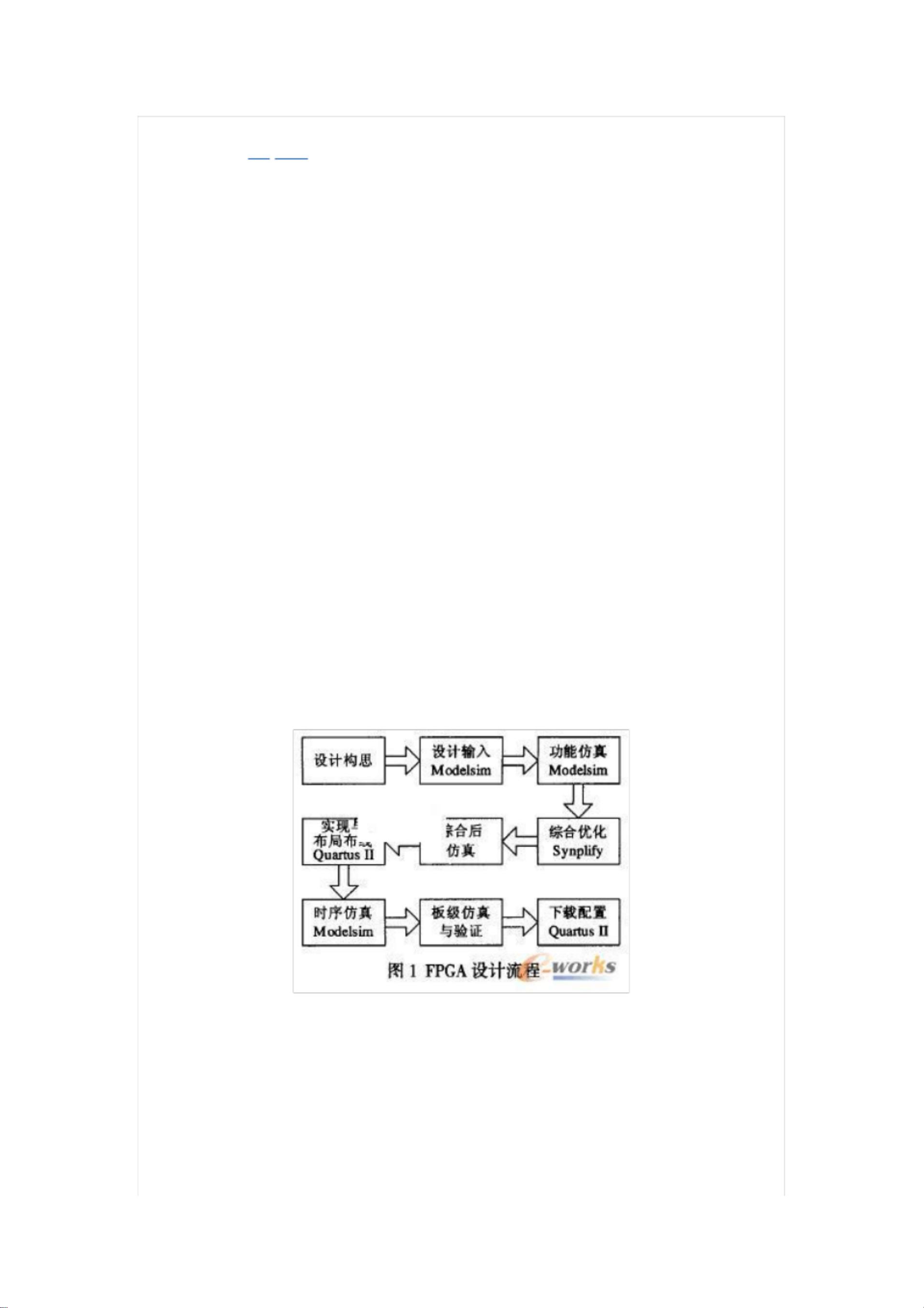

本文深入探讨了使用多种EDA工具实现FPGA设计流程的详细资料,针对FPGA(Field Programmable Gate Array,现场可编程门阵列)设计的关键环节展开系统介绍。FPGA设计流程主要包括以下几个步骤:

1. **电路设计与输入**:工程师通过硬件描述语言(HDL,如Verilog或VHDL)或原理图设计输入电路构思。HDL设计以其自顶向下、模块化和可复用的优势,成为现代大型工程设计的首选,因为它能够适应不同芯片工艺和结构的变化,便于向ASIC(Application Specific Integrated Circuit,专用集成电路)迁移。

2. **功能仿真**:设计完成后,通过专用的仿真工具,如Modelsim,进行功能仿真,验证电路的基本逻辑功能是否符合预期。

3. **综合优化**:使用EDA工具如Synplify或Quartus II进行综合,将HDL代码转化为实际的门级网表,这个过程可能会涉及逻辑优化,以减少资源消耗并提高性能。

4. **综合后仿真**:综合后的设计再次进行仿真,确保逻辑正确无误,同时评估时序性能。

5. **实现与布局布线**:完成逻辑设计后,进入布局布线阶段,将逻辑单元放置在FPGA的特定区域内,并优化信号路径以减小延迟和噪声。

6. **时序仿真与板级仿真**:时序仿真检查电路的实际运行速度,以满足系统性能要求;板级仿真则模拟真实环境中的行为,预测实际硬件的行为。

7. **调试与加载配置**:在所有仿真验证无误后,进行调试以解决潜在问题,然后将设计配置到目标FPGA器件中。

8-bit RISC CPU设计案例是本文的核心部分,作者以Altera公司的FPGA为平台,展示了如何运用Modelsim、Synplify、Quartus II等工具进行协同设计,确保整个流程的高效执行。

文章强调了在微电子学飞速发展和SoC技术的影响下,EDA工具在FPGA设计中的关键作用,表明其在当今数字系统设计领域的核心地位。通过本文,读者不仅可以掌握FPGA设计的基本流程,还能了解到如何有效地利用各种EDA工具进行高效、精确的设计。

2020-08-05 上传

2024-02-29 上传

点击了解资源详情

2020-08-02 上传

2020-11-26 上传

2022-11-16 上传

2022-11-02 上传

点击了解资源详情

点击了解资源详情

weixin_38552871

- 粉丝: 15

- 资源: 943

最新资源

- discBot

- accesslist:在渗透测试中使用的多种类型的列表的集合,收集在一个地方。 列表类型包括用户名,密码,组合,单词列表等等。

- Technologieplauscherl-Steyr:在斯太尔展示 Technologieplauscherl

- practice-code:来自各种竞争平台的Java中用于设计模式的代码

- 2021“昇腾杯”遥感影像智能处理算法大赛——语义分割赛道,冠军方案.zip

- spate141

- PositioningandFloatingElements:一种使用HMTL和CSS知识以及最近学习的float元素的实践

- Learn-Chess-Commentary

- Python库 | genomedata-1.1.0-py2.5.egg

- areddy831.github.io:按建筑风格对图像进行分类

- seash:Rust中的最小外壳

- 课程测试

- gatsby-starter-styleguide:根据您的主题UI配置立即创建样式指南页面。 零配置-只需安装主题并查看以精美的方式显示的主题UI配置

- 使用循环【迭代】来进行转化数字为中文

- ArduinoPlusPlus:无需编程即可编程arduino

- snappy:Ruby的libsnappy绑定