Xilinx Virtex-6 原理图设计手册

"Xilinx Virtex-6 原理图设计指导"

Xilinx Virtex-6系列是Xilinx公司推出的高性能FPGA(Field-Programmable Gate Array)产品线,适用于广泛的数字系统开发,包括通信、计算、图像处理等多个领域。Virtex-6提供了先进的工艺技术和丰富的内置功能,使得设计者能够实现高效能、低功耗的设计解决方案。

在Virtex-6的原理图设计中,开发者需要参考Xilinx官方提供的《Virtex-6 Libraries Guide for Schematic Designs》文档,例如UG624(v13.2),这是官方最新的版本,发布于2011年7月6日。该文档是绝对权威的设计指南,包含了一系列详细的步骤和建议,帮助设计者进行有效的VHDL或Verilog HDL设计。

此文档的使用权限受到严格限制,使用者只能将其用于与Xilinx硬件设备协同工作的设计开发中,未经Xilinx的书面许可,不得复制、分发、出版、下载、展示、发布或以任何方式传输该文档。同时,Xilinx对于因使用该文档产生的任何责任不承担任何责任。

Xilinx保留随时更改文档内容而不预先通知的权利,且没有义务纠正文档中的错误或提供更新信息。对于在使用这些信息过程中可能提供的技术支持或协助,Xilinx也不承担任何相关的责任。

“文档”是以“原样”状态提供给用户的,没有任何形式的保修。Xilinx明确否认与技术支援或协助相关的任何责任。这意味着设计者在使用Xilinx Virtex-6进行设计时,应自行承担风险,并根据文档内容进行适当的验证和测试,确保设计的正确性和稳定性。

在Virtex-6的原理图设计过程中,关键知识点包括但不限于:

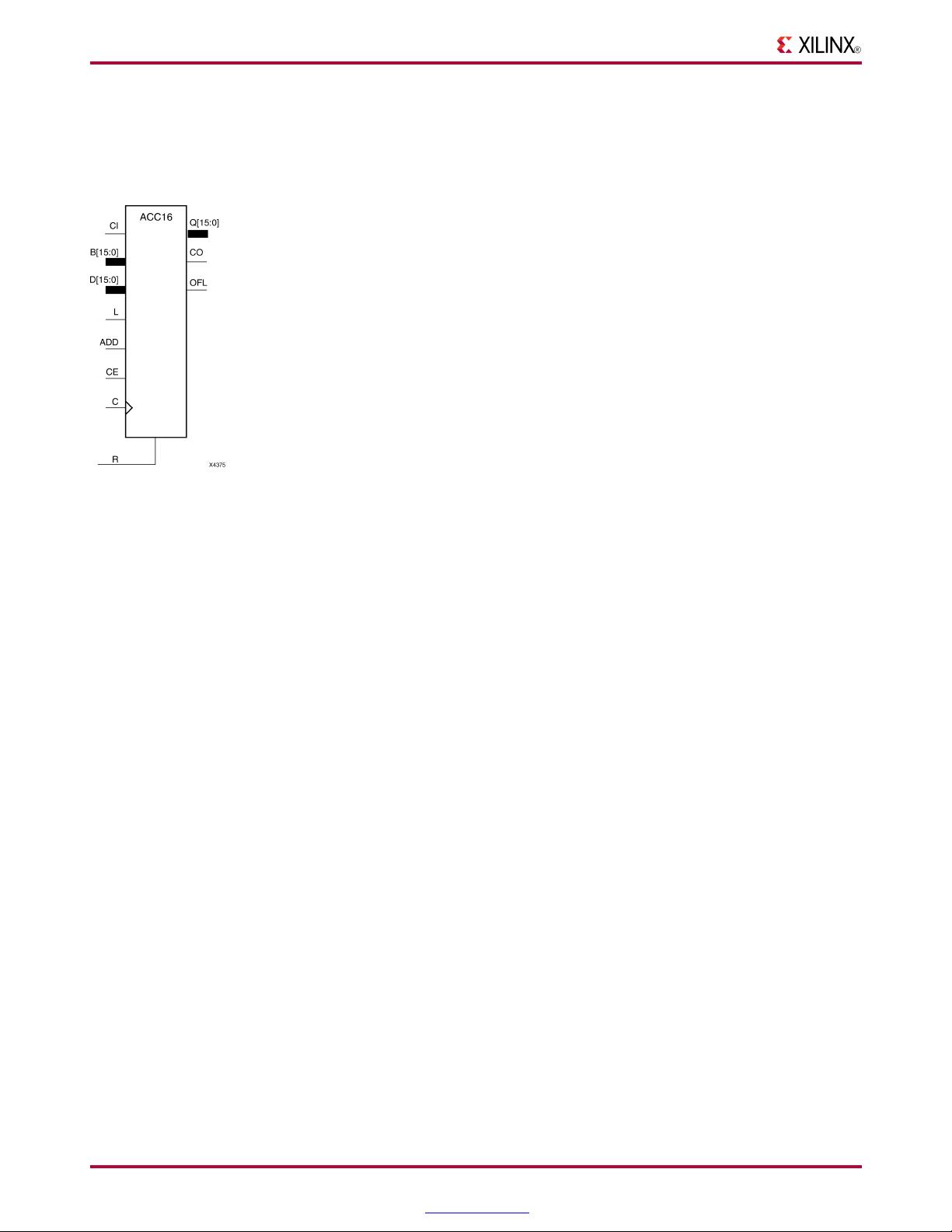

1. **逻辑单元(Logic Cells)**:理解Virtex-6 FPGA的逻辑基础单元,如查找表(LUT)、触发器等,以及如何在原理图中表示和连接它们。

2. **I/O接口**:掌握Virtex-6的输入输出资源,包括各种I/O标准(LVDS、HSTL、SSTL等),以及I/O Bank的配置。

3. **内存块(Memory Blocks)**:学习如何利用嵌入式存储器资源,如Block RAM和UltraRAM,进行高速数据存储和处理。

4. **分布式RAM**:理解如何在原理图中使用和配置分布式RAM资源。

5. **时钟管理**:学习如何设计和优化时钟网络,包括PLL(Phase-Locked Loop)和DLL(Delay-Locked Loop)的使用。

6. **路由和布线**:理解FPGA内部的互连资源,如何有效地分配和布线以达到最佳性能。

7. **功耗优化**:学习如何减少设计功耗,包括使用低功耗模式、优化电源网络等。

8. **IP核集成**:掌握如何导入和使用Xilinx的预定义IP核,如PCIe、DDR3控制器等。

9. **仿真和验证**:学习如何使用仿真工具(如ModelSim、Vivado Simulator)进行功能和时序验证。

10. **综合和实现**:理解VHDL或Verilog代码如何被综合成逻辑门级网表,以及如何通过Place & Route流程在FPGA上实现。

通过深入理解和应用上述知识点,设计师可以充分利用Virtex-6 FPGA的优势,创建高效、可靠的设计方案。在实际操作中,应严格按照文档指导进行,同时结合Xilinx的开发工具(如Vivado、ISE等)进行设计、仿真和硬件调试,确保设计的成功实施。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-04-20 上传

2018-09-11 上传

2013-10-27 上传

2023-10-10 上传

157 浏览量

点击了解资源详情

aqjinhu

- 粉丝: 0

- 资源: 2

最新资源

- Min-f-rste-hjemmeside

- turkerbulut.github.io

- Digital-monster-Program:在PC上播放数字怪物

- GenFileData.zip

- Developer Excuses-crx插件

- UdemyTest1:从 AS 创建 repos

- 深蓝色商务UI设计公司企业模板下载4910.zip

- Mybasket-backend

- sclock:电池供电的从时钟驱动器,围绕ATmega328P构建

- ayakotm-crx插件

- LEMS,c#录amr源码,c#

- 仿新乡医学院三全学院3g触屏版手机wap学校网站模板_网站开发模板含源代码(css+html+js+图样).zip

- Express-Js-Gearman-样本

- p1.sreshtanelluri

- class-33

- 使用 MATLAB 和遗传算法和直接搜索工具箱进行优化:在 2004 年 9 月 16 日举行的网络研讨会中使用的 M 文件。-matlab开发