LVPECL、LVDS、HSTL与CML间直流耦合接口详解

需积分: 46 47 浏览量

更新于2024-07-15

收藏 132KB PDF 举报

本篇报告深入探讨了在现代电子系统设计中,不同逻辑电平接口的关键技术——直流耦合(DC-Coupling)在四种常用差分信号标准之间的应用:LVPECL(低电压正发射极耦合逻辑)、LVDS(低电压差分信号)、HSTL(高速收发器逻辑)和CML(电流模式逻辑)。报告的焦点集中在这六种接口情况上,旨在解决这些逻辑电平在速度、电压范围以及噪声敏感性等方面的匹配问题。

首先,报告详细介绍了AC耦合作为基本隔离手段,但在高带宽系统中可能不适用,因为直流耦合提供了更好的信号完整性。针对每种信号标准,报告分别讨论:

1. **LVPECL** (LVPECL到LVPECL接口):这部分重点阐述了如何确保低电压正偏置下的电荷泵或变压器等器件在两个LVPECL信号之间提供有效的直流耦合,以减少信号失真和噪声的影响。

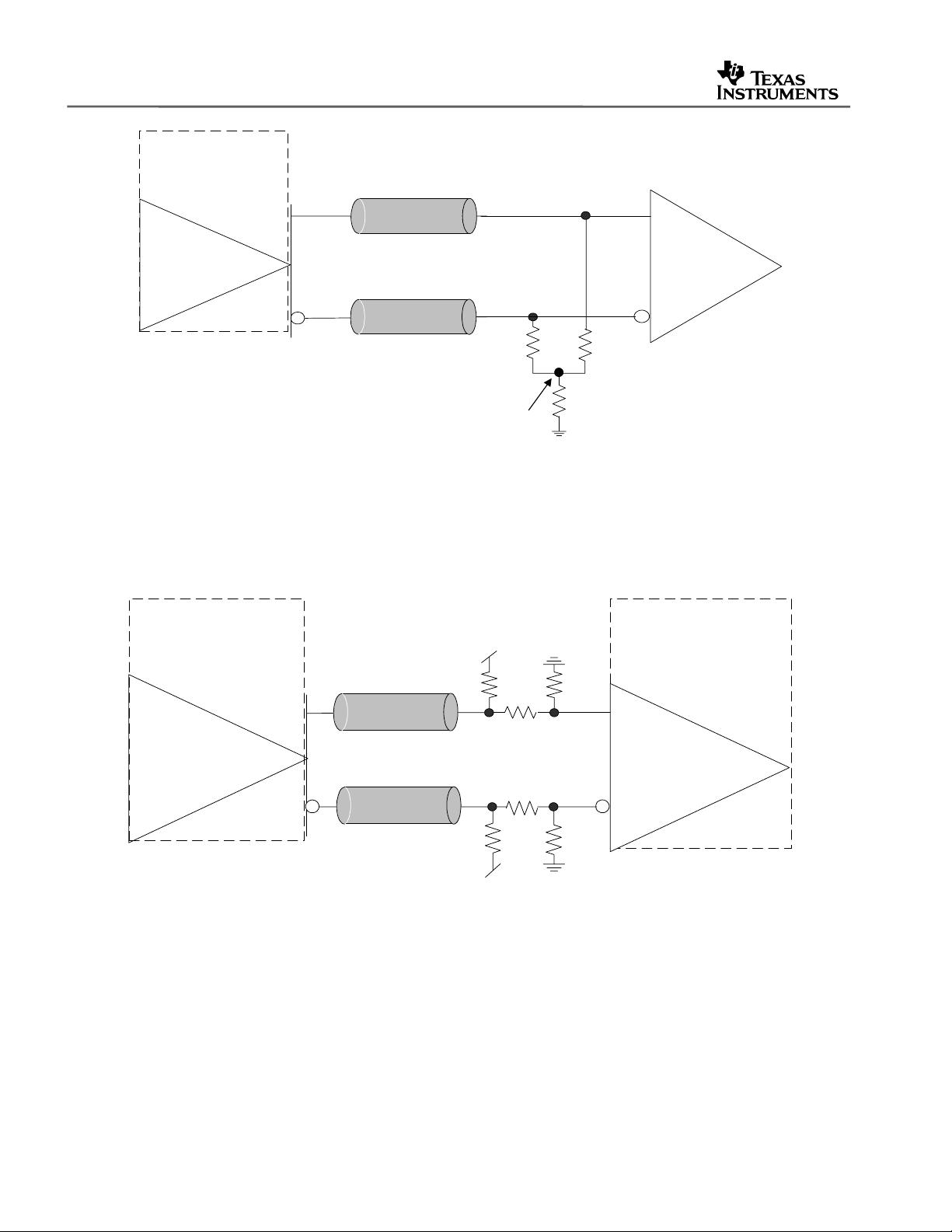

2. **LVDS**:LVDS接口涉及两种情况,一是LVPECL与LVDS之间的转换,包括无芯片内终止和有终止的方案,目的是优化数据传输速率和信号质量。第二种情况是LVDS与其他逻辑电平之间的直接耦合,如LVDS到LVPECL,以兼容不同设备的驱动能力。

3. **CML**:CML逻辑以其低阻抗特性而闻名,报告会探讨LVPECL到CML的耦合策略,包括可能需要的转换电路,以适应CML的低电压工作模式。

4. **HSTL**:HSTL通常用于高速应用,报告分析了如何通过直流耦合有效地将LVPECL信号与HSTL信号同步,以实现高效的数据传输。

此外,报告还包含一系列图表,如输入输出参数、不同信号类型间的耦合电路示意图,帮助设计师理解每种接口的具体实现方法和注意事项。参考文献部分列出了相关的研究和标准,以便读者进一步深入学习和了解相关领域的最新进展。

这篇报告对于设计者来说是一份宝贵的资源,它提供了在实际应用中实现直流耦合,以确保不同逻辑电平之间的无缝通信和性能优化的关键技术和实践指南。

2306 浏览量

383 浏览量

338 浏览量

229 浏览量

163 浏览量

1629 浏览量

2022-07-15 上传

959 浏览量

2021-06-12 上传

tianyi19901

- 粉丝: 2

最新资源

- DeepFreeze密码移除工具6.x版本使用教程

- MQ2烟雾传感器无线报警器项目解析

- Android实现消息推送技术:WebSocket的运用解析

- 利用jQuery插件自定义制作酷似Flash的广告横幅通栏

- 自定义滚动时间选择器,轻松转换为Jar包

- Python环境下pyuvs-rt模块的使用与应用

- DLL文件导出函数查看器 - 查看DLL函数名称

- Laravel框架深度解析:开发者的创造力与学习资源

- 实现滚动屏幕背景固定,提升网页高端视觉效果

- 遗传算法解决0-1背包问题

- 必备nagios插件压缩包:实现监控的关键

- Asp.Net2.0 Data Tutorial全集深度解析

- Flutter文本分割插件flutter_break_iterator入门与实践

- GD Spi Flash存储器的详细技术手册

- 深入解析MyBatis PageHelper分页插件的使用与原理

- DELPHI实现斗地主游戏设计及半成品源码分析