8进制同步计数器设计:J-K触发器应用与步骤详解

需积分: 5 132 浏览量

更新于2024-08-03

收藏 1.34MB PPTX 举报

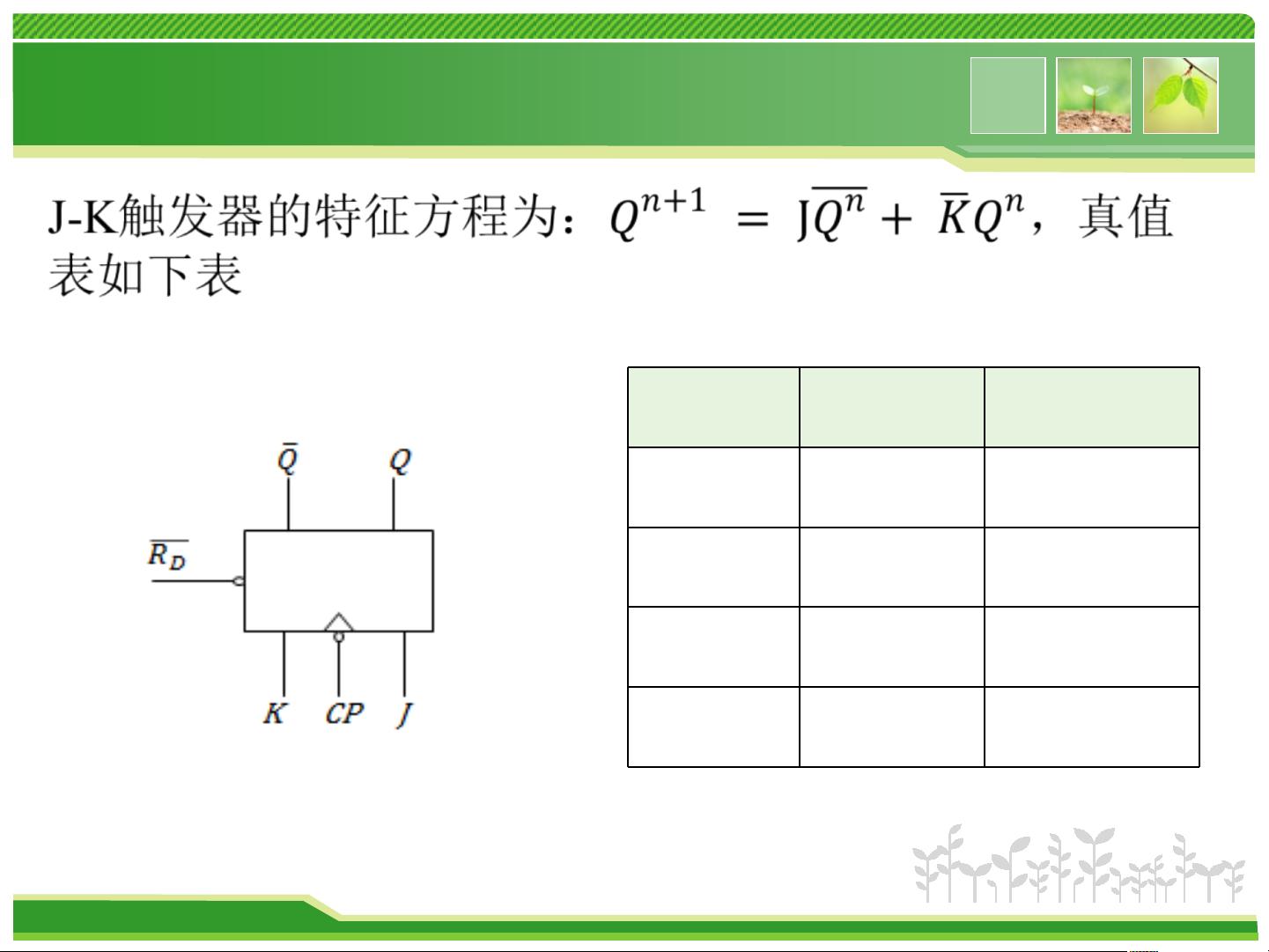

实验8 同步计数器的设计是一个针对J-K触发器应用的实践课程,主要目的是让学生深入理解并掌握这种基本逻辑元件在计数器设计中的运用。在这个实验中,学生将设计一个特殊的12进制计数器,采用8421编码非BCD码系统,仅允许使用1010及其后续码表示十进制数。设计的关键步骤包括以下几个部分:

1. **实验目标**:熟悉J-K触发器的基本逻辑功能,并将其应用到实际的计数器设计中,增强对时序逻辑的理解。

2. **原理概述**:设计过程包括简化的设计步骤,例如先确定所需触发器的数量,然后构建状态转换图,绘制状态转换表,进而推导出J-K触发器的状态方程和驱动方程,以确保电路能够按照预期工作。

3. **实验内容**:

- **静态检查**:使用逻辑开关模拟输入,通过观察输出和接“0~1”显示器来验证电路是否正常运行,触发器CP端接单脉冲。

- **动态检查**:增加连续脉冲,利用示波器观察输出波形,确保在连续计数时电路无误。

- **器件选择**:实验中使用了74LS00、74LS08、74LS109等双极型互补金属氧化物半导体(CMOS)集成逻辑门和触发器,这些器件的选择根据设计需求决定。

4. **设计过程**:

- **触发器数目确定**:根据计数器的进制和编码方式计算所需的触发器数量。

- **状态转换与表绘制**:构建计数器的状态转换图,以此为基础制作状态转换表,反映每个输入组合对应的状态变化。

- **状态方程与驱动方程**:基于状态转换表,确定J-K触发器的状态更新规则和驱动信号的计算。

- **自启动性检查**:确认电路是否能在初始状态下自动进入下一个计数状态。

- **逻辑图绘制**:整理所有逻辑关系,形成清晰的电路图。

5. **实验设备与所用器件**:实验中涉及到了74LS00(4输入与非门)、74LS08(3-8线译码器)、74LS109(同步二进制计数器)等基础逻辑器件,用于构建不同部分的电路结构。

6. **实验报告要求**:实验报告需包含实验目的、实验内容、使用的设备和器件列表、设计过程的具体细节(如状态转换表、卡诺图、状态方程和驱动方程、逻辑图)、静态和动态检查的结果以及相关的波形图,以便于评估实验成果和理解。

通过这个实验,学生不仅提升了设计和分析同步计数器的能力,还巩固了数字逻辑电路的实际操作技巧,以及对时序逻辑深入的理解。

2021-10-28 上传

2021-09-30 上传

130 浏览量

2021-10-05 上传

2021-10-02 上传

2021-09-30 上传

2021-10-11 上传

2021-10-03 上传

2021-10-02 上传

没想到主角也会颜艺。。。

- 粉丝: 0

最新资源

- imgix-emacs: Emacs内图像编辑与imgix URL生成工具

- Python实现多功能聊天室:单聊群聊与智能回复

- 五参数逻辑回归与数据点拟合技巧

- 微策略MSTR安装与使用教程详解

- BootcampX技术训练营

- SMT转DIP分线板设计与面包板原型制作指南

- YYBenchmarkFFT:iOS/OSX FFT基准测试工具发布

- PythonDjango与NextJS构建的个人博客网站指南

- STM32控制433MHz SX1262TR4-GC无线模块完整设计资料

- 易语言实现仿SUI开关滑动效果源码教程

- 易语言寻路算法源码深度解析

- Sanity-typed-queries:打造健壮的零依赖类型化查询解决方案

- CSSSTATS可视化入门套件使用指南

- DL_NG_1.4数据集压缩包解析与使用指南

- 刷卡程序及makefile编写教程

- Unreal Engine 4完整视频教学教程中文版208集