FPGA加速μC/OS-II任务管理:硬件设计与性能提升

129 浏览量

更新于2024-08-30

收藏 330KB PDF 举报

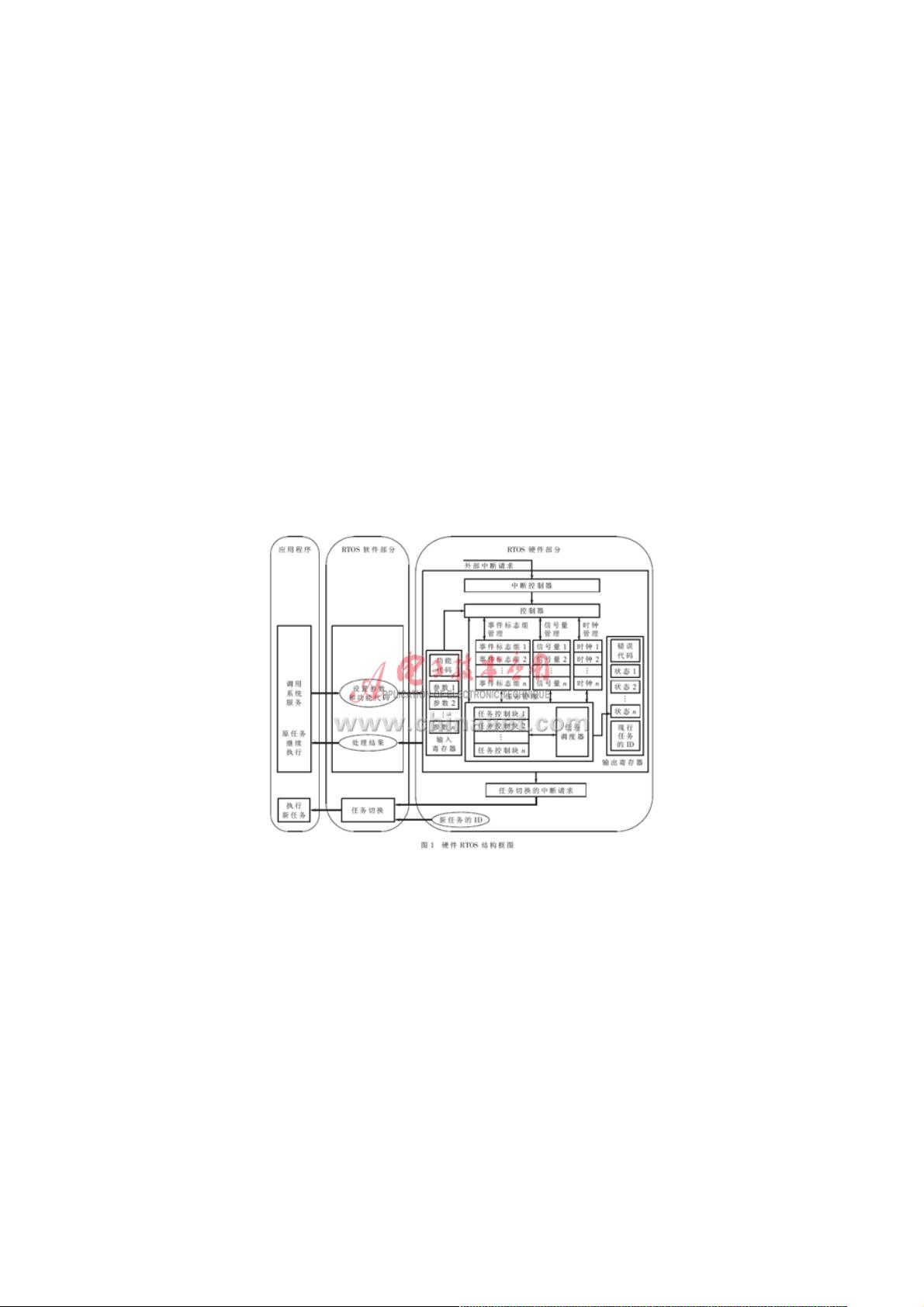

本文主要探讨了如何通过基于FPGA的硬件设计来解决实时操作系统(RTOS)中因任务管理开销导致的应用程序性能下降问题。μC/OS-II是本文选择的特定RTOS实例,其任务管理模块被硬件化以提升系统性能。

首先,传统的优化方法如改进调度算法和提升处理器速度虽然有助于提高实时性,但已无法满足现代硬件的发展需求。为了充分利用多任务并行性,设计者提出了基于FPGA的解决方案。硬件化的μC/OS-II任务管理模块包括两个关键部分:一是基于片内寄存器的任务控制块(TCB),它存储每个任务的状态信息,如优先级和状态标志;二是基于组合电路的任务调度器,它负责根据任务优先级实时地决定任务执行顺序。

设计过程中,作者采用了VHDL硬件描述语言,这是一种强大的工具,用于编写硬件描述,使得设计过程更加清晰和可验证。通过ISE 8.2软件进行时序仿真,确保了设计的正确性和有效性。硬件实现是在Xilinx公司的Virtex-II Pro FPGA板上完成的,这一步验证了设计的可移植性和实际应用潜力。

硬件RTOS的设计理念是将原本由软件执行的任务管理功能转换为硬件,以实现更高的处理速度和更低的CPU开销。硬件函数通过数据总线与处理器并行工作,避免了软件函数的指令执行周期,从而提高了系统的响应速度和并发性。输入输出寄存器负责接收和传递数据,中断控制器则管理任务间的切换,而控制器则协调整个硬件RTOS的运行。

总结来说,这篇论文提出了一种创新的方法,即利用FPGA技术将μC/OS-II的任务管理模块硬件化,以优化RTOS的性能和实时性,这对于现代嵌入式系统和实时计算任务具有重要意义。通过硬件化的手段,设计者能够更好地利用硬件资源,提升系统的效率和可扩展性,为未来的实时系统设计提供了新的思考方向。

点击了解资源详情

点击了解资源详情

2020-10-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38705558

- 粉丝: 4

- 资源: 944

最新资源

- 俄罗斯RTSD数据集实现交通标志实时检测

- 易语言开发的文件批量改名工具使用Ex_Dui美化界面

- 爱心援助动态网页教程:前端开发实战指南

- 复旦微电子数字电路课件4章同步时序电路详解

- Dylan Manley的编程投资组合登录页面设计介绍

- Python实现H3K4me3与H3K27ac表观遗传标记域长度分析

- 易语言开源播放器项目:简易界面与强大的音频支持

- 介绍rxtx2.2全系统环境下的Java版本使用

- ZStack-CC2530 半开源协议栈使用与安装指南

- 易语言实现的八斗平台与淘宝评论采集软件开发

- Christiano响应式网站项目设计与技术特点

- QT图形框架中QGraphicRectItem的插入与缩放技术

- 组合逻辑电路深入解析与习题教程

- Vue+ECharts实现中国地图3D展示与交互功能

- MiSTer_MAME_SCRIPTS:自动下载MAME与HBMAME脚本指南

- 前端技术精髓:构建响应式盆栽展示网站