A 24GHz Low Power and Low Phase Noise PLL

Frequency Synthesizer with Constant K

VCO

for

60GHz Wireless Applications

Jun Luo, Lei Zhang, Member, IEEE, Li Zhang, Yan Wang and Zhiping Yu, Fellow, IEEE

Abstract —In this paper, a fully integrated 24GHz

integer-N PLL for a 60GHz wireless transceiver is presented.

A VCO with tail-feedback technique is used to improve the

phase noise by modulating the tail current, and a switched

varactor array is also adopted together with a switched

capacitor array to compensate the variation of K

VCO

over

different bands. Moreover, benefiting from the careful

optimization of CML pre-scaling divider, the PLL operates

correctly when VCO buffer is turned off, coming up with an

extremely low power. The whole PLL is fabricated in

standard 90-nm process. Measurement shows that the VCO

achieves a phase noise of -102dBc/Hz@1MHz offset with a

tuning range of over 16%. The K

VCO

variation over all bands

is less than 16%. In close-loop operation mode the PLL

shows an integrated phase error of 3.3°rms (from 100kHz to

100MHz) over prescribed frequency bands, and a total power

dissipation of only 26mW.

Index Terms —PLL, VCO, low power, phase noise, 24GHz.

I. INTRODUCTION

The wide unlicensed 7GHz bandwidth around 60GHz

enables high speed wireless communication with multiple

Gbps data rate, which has increasingly drawn attentions

from both academia and industry [1]. Phase-locked Loop

(PLL), is a key building block for frequency synthesis in

most of the transceivers. A voltage-controlled oscillator

(VCO) operating at high frequency consumes a large

power and suffers from a narrow tuning range, especially

for millimeter-wave (mm-wave) applications [2].

Moreover, a large power is also consumed by the pre-

scaling frequency dividers interfacing with VCO in a PLL

system. Considering the power consumption and local

oscillation (LO) distribution, a 24GHz PLL serving for

LO frequency synthesis is employed in a super-heterodyne

60GHz transceiver, in which the first and second LO

signals are generated by a doubler and a divider following

the PLL, respectively.

Even at 24GHz band, PLL is still power hungry. There

are many reported works on the low power design of VCO

and pre-scaling dividers at mm-wave frequency [3].

However, few work focuses on the co-optimization of the

feed-back chain composed of VCO buffer and the first

pre-scaling divider which is power hungry. Moreover, due

to the PLL stability requirement over a wide band, e.g.

60GHz applications, maintaining a constant loop

bandwidth (LBW) is mandatory, which calls for a constant

K

VCO

. Although it has drawn attentions in low frequency

designs [4], few work has been reported in mm-wave

PLLs.

In this paper, a 24GHz 4 channel integer-N PLL is

designed. On one hand, a switched varactor array is

adopted together a switched capacitor array to compensate

the variation of K

VCO

over different bands, and tail-

feedback in VCO is also incorporated to improve the

phase noise. On the other hand, analysis and design of

CML divider based on second-order approximation is

proposed for power and operation range co-optimization.

Measurement shows that even the VCO buffer is turned

off, the PLL can still work correctly, coming up with an

extremely low power.

This paper is organized as follows: Section II discusses

the circuit design considerations and proposed techniques

of the PLL. Section III presents the measurement results,

and finally the conclusions are drawn in Section IV.

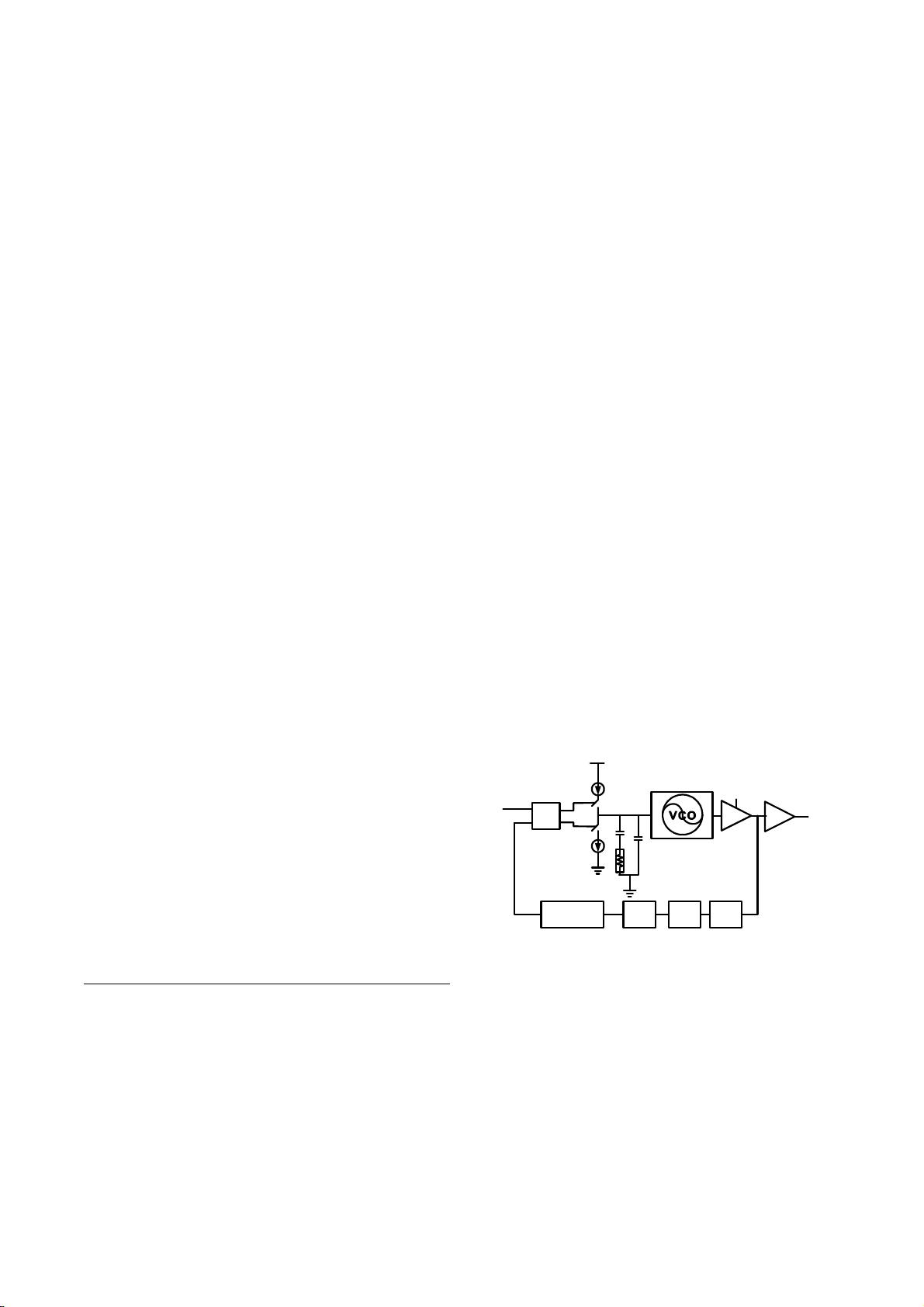

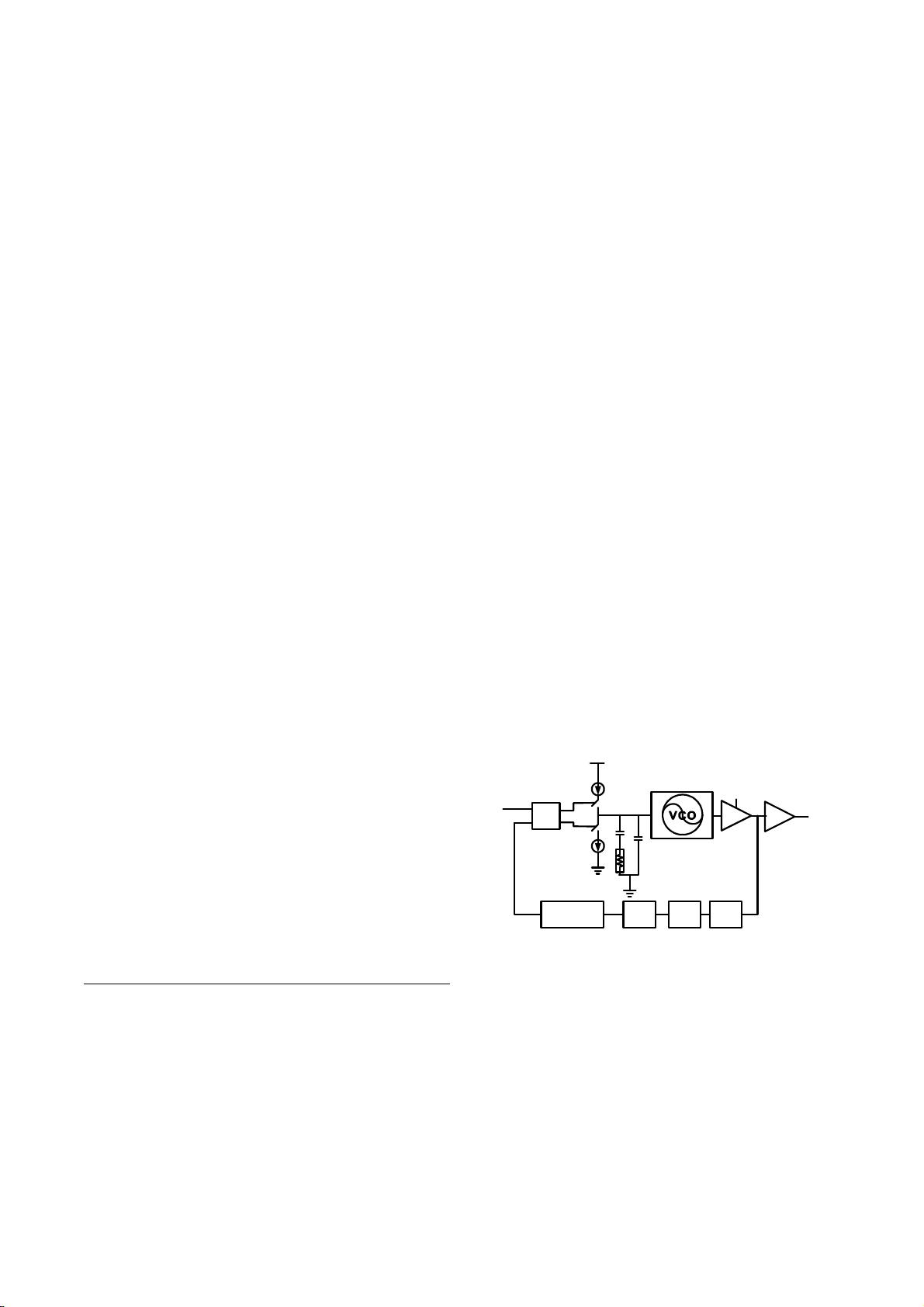

PFD

CML_

/2

MMD_DIV_27

~30

Fref=108MHz

R1

C1

R2

CML_

/2

CML

/2

Buf_for_test

23.5GHz~28.2GHz

VCO_Buf

Fig. 1. Proposed 24GHz integer-N PLL with frequency planning.

II. CIRCUIT DESIGN OF THE PLL SYNTHESIZER

The 24GHz PLL is designed with an integer-N

topology for the purpose of simple tuning and superior

phase noise as shown in Fig. 1. A VCO buffer, whose

supply voltage can be tuned, is connected to the VCO,

with a tuning range from 23.5GHz to 28.2GHz. Three

CML divide-by-2 dividers, serving for pre-scaling, are

This work is supported by National 863 Program of Chin

2011AA010202 and 2015AA011307, National Natural Science

Foundation of China under grants 61101001 and 61204026, an

Tsinghua University Initiative Scientific Research Program.

The authors are with Institute of Microelectronics, Tsinghu

University, Beijing 100084, China (e-mail: zhang.lei@tsinghua.edu.cn).

978-1-4799-8391-9/15/$31.00 ©2015 IEEE 2840