Verilog实现的有限状态机在数字电路控制中的优势

需积分: 5 59 浏览量

更新于2024-07-09

收藏 1.12MB PDF 举报

"有限状态机与Verilog设计"

有限状态机(Finite State Machine, FSM)是数字电路设计中的一种重要概念,它用于实现控制逻辑,特别是在可编程逻辑器件(如FPGA或 CPLD)中。FSM通过状态转移来实现特定的功能,类似于CPU中的指令执行流程,但更加灵活且适用于特定任务。

1. FSM的基本概念:

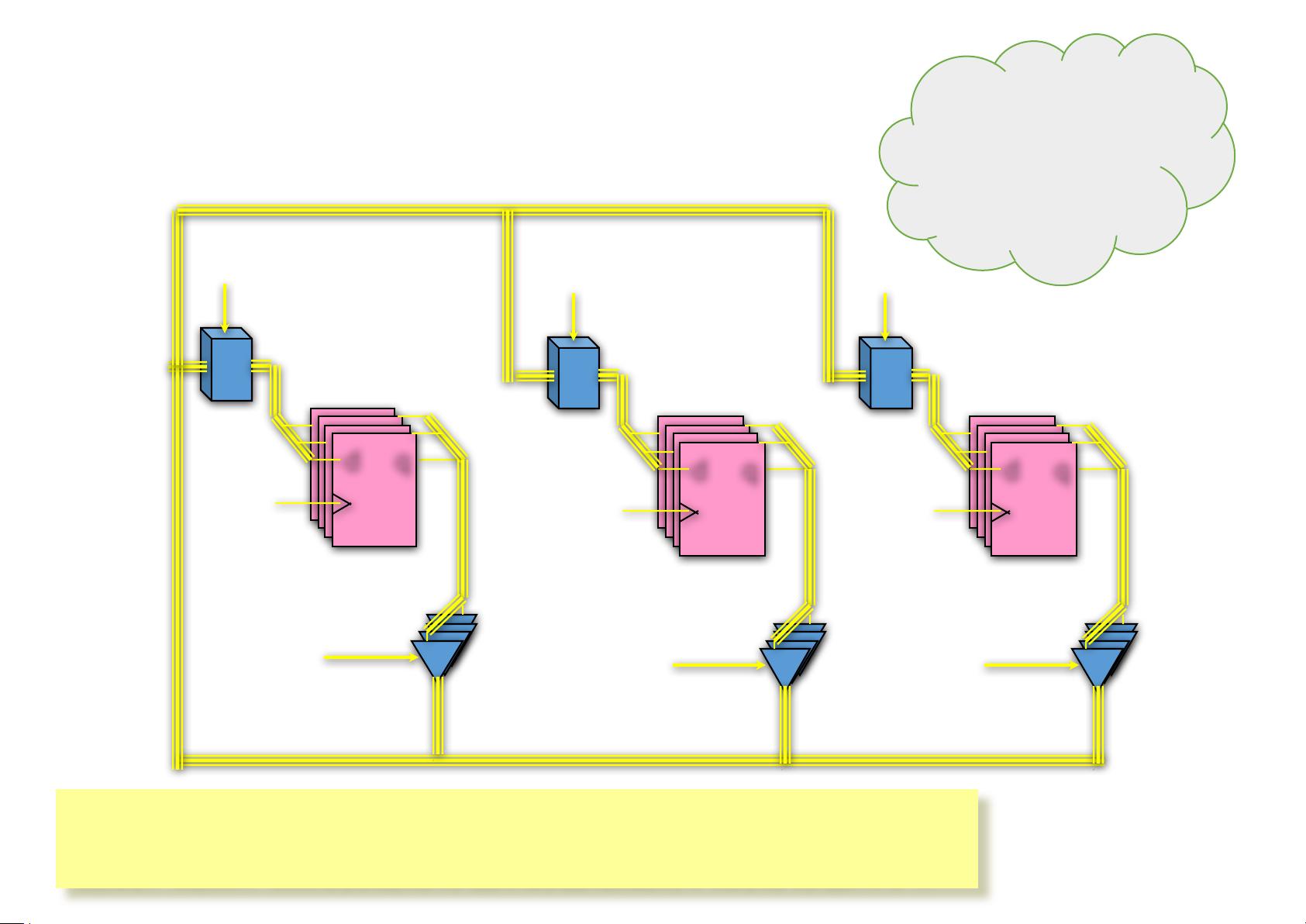

- FSM是一种数学模型,它通过一组预定义的状态和状态之间的转换来描述系统的动态行为。在数字电路中,这些状态通常由一组寄存器(例如D触发器)存储,而状态转移则由组合逻辑电路决定。

- FSM分为同步和异步两种类型,同步FSM以时钟信号为基准,状态在时钟边沿变化,而异步FSM则不受时钟信号约束,状态变化可能在任何时刻发生。

2. FSM与CPU功能比较:

- CPU依赖于操作指令和硬件操作单元来执行任务,而FSM则是通过状态转移表或图来定义其行为。

- 在可编程逻辑器件中,用Verilog等硬件描述语言(HDL)编写的FSM可以生成高效、快速且资源利用率高的设计,相比CPU实现,具有更好的性能。

3. 使用FSM的原因:

- FSM克服了纯硬件控制的灵活性不足,其结构简单,易于理解和设计。

- FSM的HDL表示多样化,可以方便地描述复杂控制逻辑。

- 在高速运算和控制场景下,FSM能提供更优的解决方案,同时在可靠性方面也表现出色。

4. 数据流动控制:

- FSM在数字系统中起到关键作用,通过精确控制时钟信号和状态转换,确保数据在寄存器和逻辑电路间的有序流动,避免冒险和竞争现象,解决时延问题。

- FSM的设计包括记忆当前状态、在时钟边沿进行状态转移以及根据状态改变控制逻辑电路的开关。

5. Verilog实现:

- Verilog是一种用于描述数字系统的HDL,可以用来定义和实现FSM。通过定义状态变量、状态转移条件和输出逻辑,可以生成对应的FSM硬件逻辑。

6. 设计原则:

- FSM的设计需要考虑状态编码、状态转移图或表、初始状态、终止状态以及输入和输出的映射。

- 为了确保正确性和避免竞争冒险,必须确保所有状态变化都在时钟边沿,并且状态的改变取决于输入条件和当前状态。

有限状态机是数字电路设计中的核心工具,尤其在Verilog等HDL中,它能够实现复杂控制逻辑,提供高效、可靠且灵活的设计方案。通过深入理解FSM的工作原理和Verilog语法,工程师可以创建出高性能的数字系统。

656 浏览量

220 浏览量

195 浏览量

942 浏览量

2022-06-20 上传

109 浏览量

108 浏览量

116 浏览量

不拖延症

- 粉丝: 0

最新资源

- Python大数据应用教程:基础教学课件

- Android事件分发库:对象池与接口回调实现指南

- C#开发的斗地主网络版游戏特色解析

- 微信小程序地图功能DEMO展示:高德API应用实例

- 构建游戏排行榜API:Azure Functions和Cosmos DB的结合

- 实时监控系统进程CPU占用率方法与源代码解析

- 企业商务谈判网站模板及技术源码资源合集

- 实现Webpack构建后自动上传至Amazon S3

- 简单JavaScript小计算器的制作教程

- ASP.NET中jQuery EasyUI应用与示例解析

- C语言实现AES与DES加密算法源码

- 开源项目实现复古游戏机控制器输入记录与回放

- 掌握Android与iOS异步绘制显示工具类开发

- JAVA入门基础与多线程聊天售票系统教程

- VB API实现串口通信的调试方法及源码解析

- 基于C#的仓库管理系统设计与数据库结构分析