EDA数字秒表设计与实现

需积分: 25 164 浏览量

更新于2024-07-24

1

收藏 495KB DOC 举报

"EDA数字秒表的设计报告,涵盖了系统功能要求、总体框图以及部分模块的设计,如模60计数器和模100计数器,旨在实现精确到0.01秒的计时功能,具备启/停、复位功能。报告由郑州科技学院电子科学与技术专业的学生李阳完成,指导教师为赵明冬。"

在这个EDA数字秒表的设计中,主要目标是创建一个能够精确计时并显示时间的设备,最大计时范围为1小时,精度达到0.01秒。秒表应具备基本的启/停和复位功能,以便用户控制和重置计时。设计的核心组件包括六十进制计数器、二十四进制计数器、分频器、LED显示模块,以及各种控制逻辑。

在总体框图中,可以看到系统依赖于三个主要输入:启/停开关(en),时钟信号(clk)和复位开关(reset)。这些信号控制着系统的运行状态。模60计数器和模100计数器用于计算分钟和秒,确保时间的正确累计。分频器将实验室提供的1kHz时钟信号转化为100Hz的时钟,满足0.01秒精度的计时需求。复位控制模块则负责在需要时重置计数器。译码器将二进制数据转换为适合LED显示的七段编码,使得时间能够直观地呈现给用户。防抖模块则用于处理用户按键操作时可能出现的抖动问题,确保信号的稳定。状态变换模块则处理按键操作后的信号转换和保持,保证系统对用户输入的正确响应。

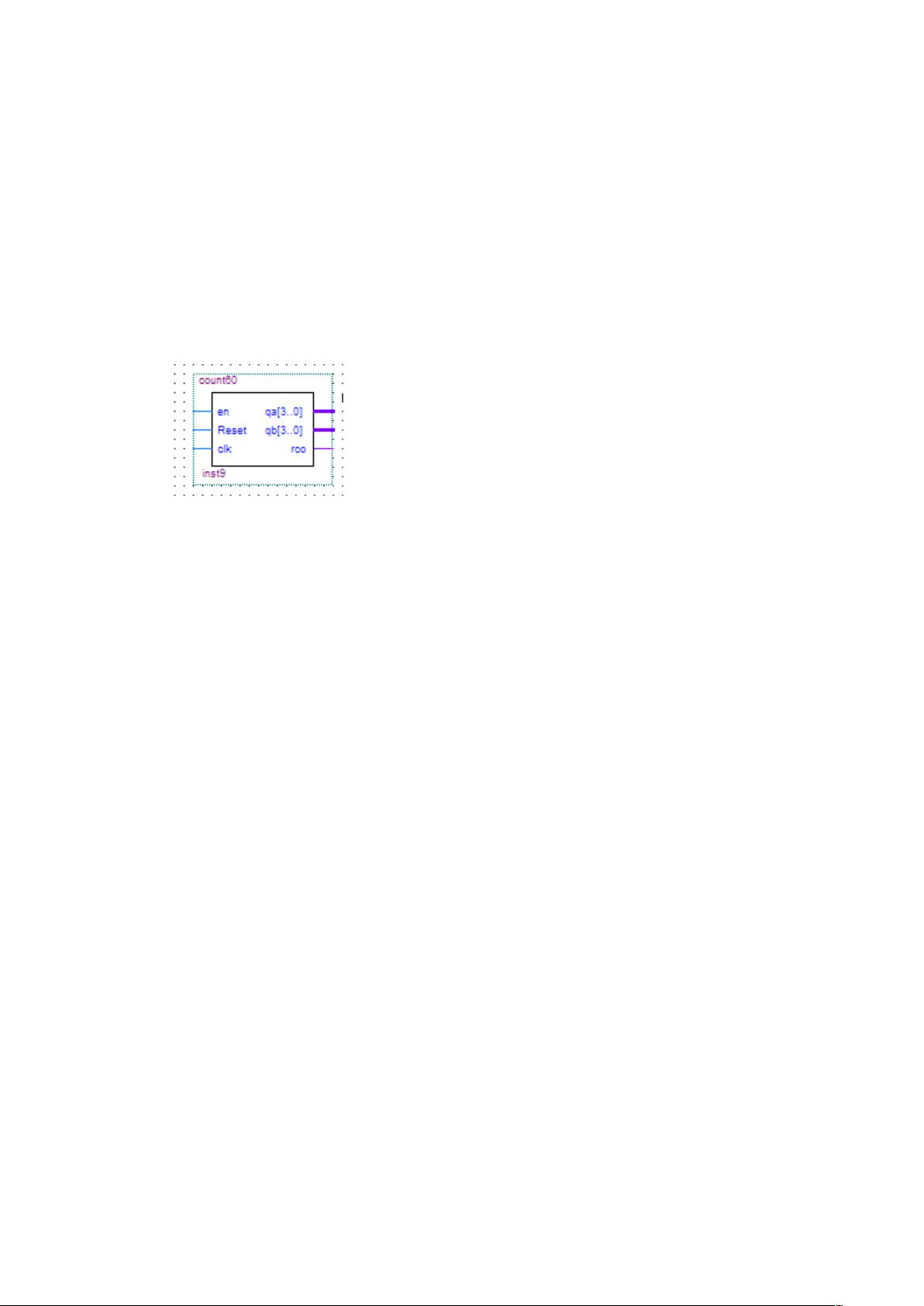

在模60计数器的VHDL源程序片段中,我们可以看到定义了实体`count60`,它有输入信号en, Reset, clk和输出信号qa, qb, rco。这个模块使用了IEEE标准库中的`STD_LOGIC_1164`和`STD_LOGIC_UNSIGNED`,这表明它是基于逻辑门级的描述,用于实现60进制的计数逻辑。

这个EDA数字秒表的设计是一个综合运用数字逻辑、计数器、分频器、译码器和控制逻辑的项目,展示了电子科学与技术领域的基础知识和实践应用。通过这样的设计,学生可以深入理解数字系统的工作原理,同时锻炼了实际的硬件描述语言编程技能。

772 浏览量

2024-10-22 上传

201 浏览量

151 浏览量

309 浏览量

679 浏览量

2023-08-22 上传

没想好115

- 粉丝: 0

- 资源: 1

最新资源

- Spring Live (160页)

- iBatis Developer's Guide中文版

- Spring iBatis Learning Notes

- Verilog Hardware Description Language

- 《linux完全命令手册》(Linux Complete Command Reference)

- 数控机床RS232通讯接口及参数介绍

- 多型与虚拟.pdf 中文版

- WindowsCE内核简介

- 经典C源程序100例

- 初学者c51学习教程

- GoF 23种设计模式解析附C++实现源码.pdf

- c++编程手册,题目

- Windows 2000 安全配置

- 中南大学微机原理课件

- UML参考手册 UML Reference

- jsp跳转的五种方式