"数字集成电路逻辑综合原理与设计:Verilog HDL编程技巧和优化流程详解"

版权申诉

84 浏览量

更新于2024-02-25

收藏 3.39MB PDF 举报

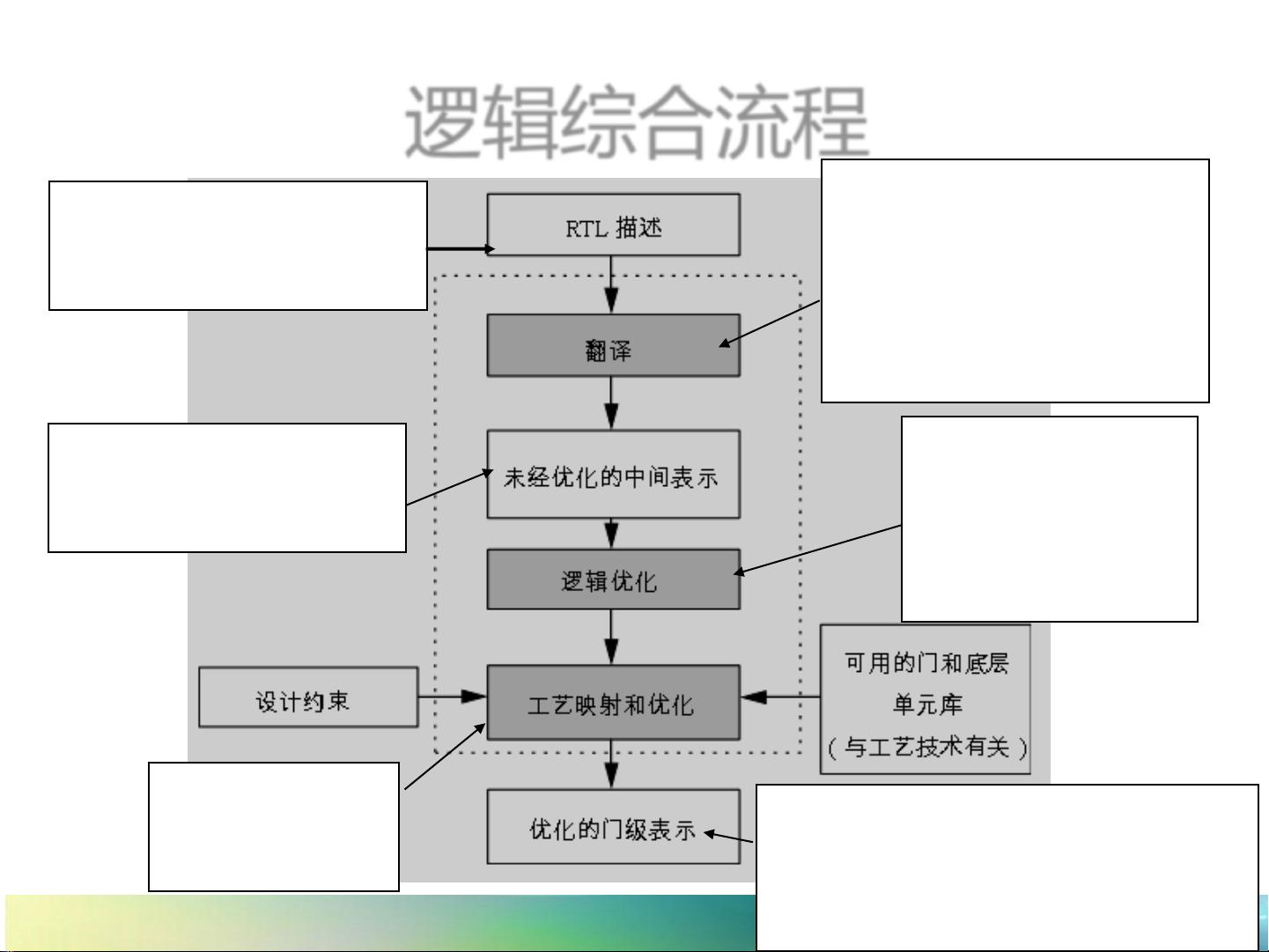

本节课程《数字集成电路原理与设计》的主题是逻辑综合,主讲人是姜小波。在本章中,我们将深入了解逻辑综合的定义、方法和流程,包括RTL描述、转换、优化、设计约束、属性设置、工艺库和门级表示。我们还将学习逻辑综合工具和Verilog HDL综合的相关知识,并探讨设计技巧和综合的层次。

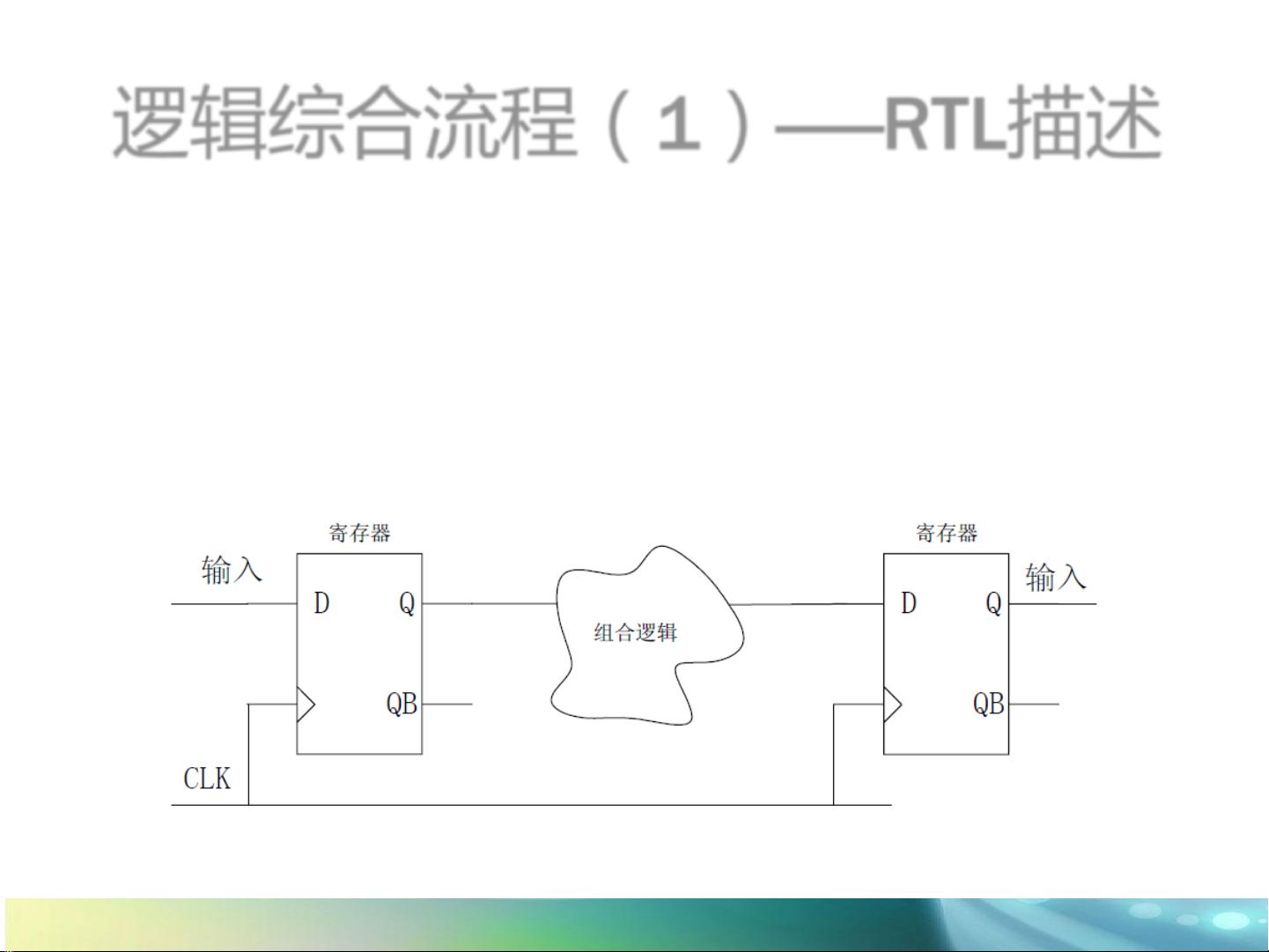

逻辑综合是根据设计应实现的功能与约束条件,通过计算机的优化处理,获得一个满足要求的设计方案的过程。在数字系统中,可以在多个层次上描述,包括算法层、寄存器传输层、逻辑层、电路层和版图层。通常,综合可以分为高层次综合、逻辑综合和版图综合三个层次。本课程主要关注从算法级行为描述到寄存器传输级结构描述的逻辑综合技术。

高层次综合是从算法级的行为描述转换到寄存器传输级的描述。在高层次综合过程中,我们需要了解算法级和寄存器传输级之间的关系,并将行为特性转换为结构特性。高层次综合技术对于提高数字集成电路设计的效率和性能至关重要。

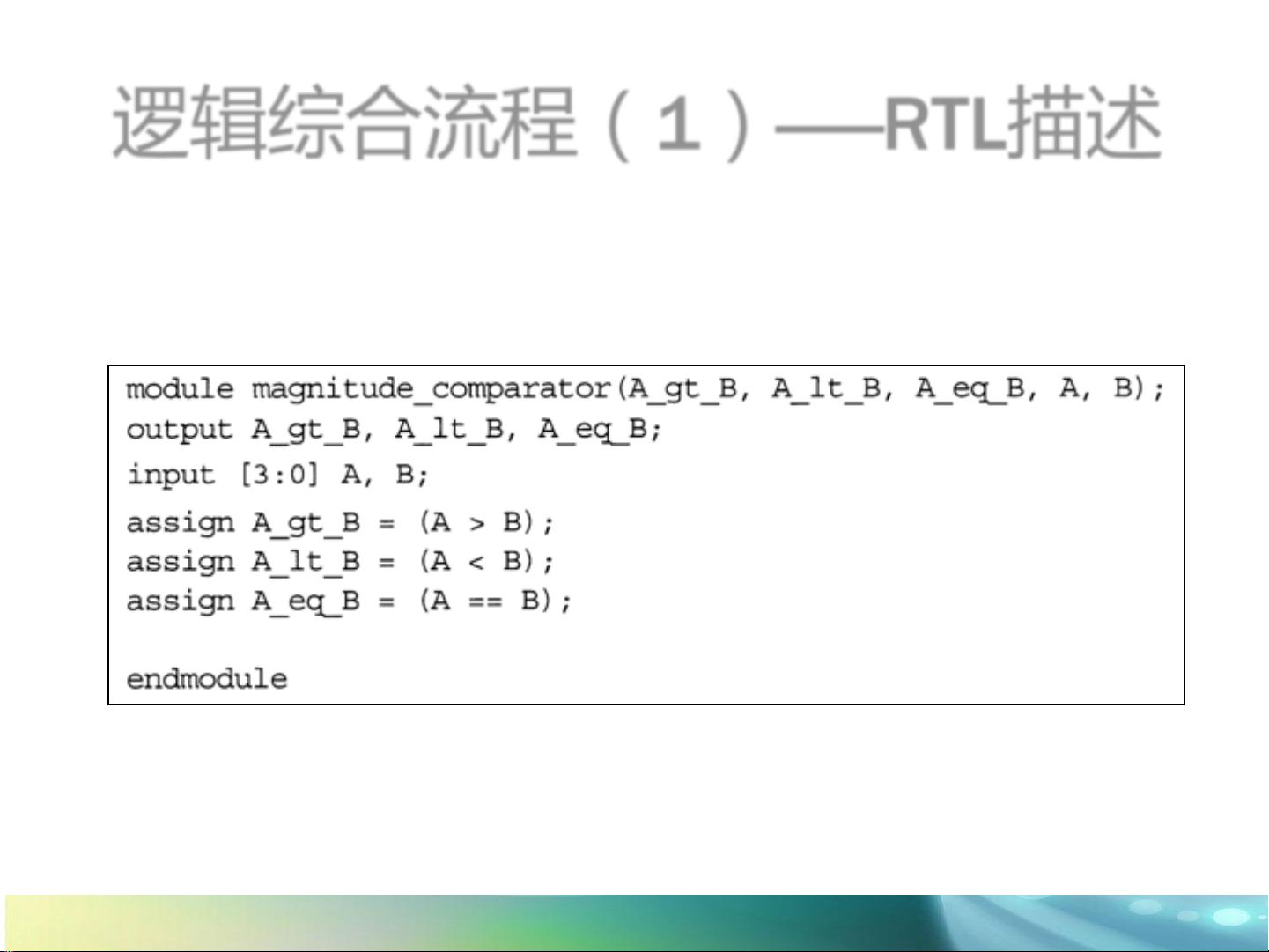

在学习逻辑综合的过程中,我们需要掌握RTL描述、转换和优化的方法。RTL描述是采用Verilog HDL等硬件描述语言进行电路逻辑的描述,转换是将RTL描述转换为逻辑门级的电路描述,而优化则是在转换的基础上对电路进行优化,以满足不同的约束条件。

逻辑综合的方法包括手动和自动两种。手动综合需要设计人员根据实际情况进行逻辑电路的设计和优化,而自动综合则可以通过计算机工具来实现。在实际的数字集成电路设计中,通常会采用自动逻辑综合工具,以提高设计效率和准确性。

除了逻辑综合的基本方法和流程外,我们还需要了解设计约束、属性设置和工艺库的相关知识。设计约束是指在逻辑综合过程中,为了满足电路性能和功耗等要求而设置的条件,属性设置则是针对特定的设计需求而设置的相关属性,而工艺库则是包含了标准单元库和时序模型库等信息的数据库。

最后,我们会通过实例来学习Verilog HDL综合的相关知识,并探讨设计技巧和综合的层次。Verilog HDL是一种用于数字电路描述和硬件设计的硬件描述语言,通过学习Verilog HDL的综合技术和设计技巧,可以帮助我们更好地理解逻辑综合的过程,并提高设计的效率和准确性。

总的来说,逻辑综合是数字集成电路设计过程中至关重要的一环,通过学习逻辑综合的基本方法和流程,以及掌握相关工具和技巧,可以帮助我们更好地理解和应用逻辑综合技术,从而提高数字集成电路的设计效率和性能。

点击了解资源详情

2021-04-06 上传

2020-10-24 上传

2022-06-24 上传

2022-12-10 上传

2022-11-29 上传

智慧安全方案

- 粉丝: 3814

- 资源: 59万+

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析