SystemVerilog VMM验证方法学详解

"VMM (Virtual Machine Monitor) 是一种针对SystemVerilog的验证方法学,旨在帮助工程师构建高效、可重用的验证环境,以应对复杂的SoC(System on Chip)设计验证。VMM方法学结合了SystemVerilog的语言特性,如约束随机化、覆盖率驱动验证、断言等,来提升验证的全面性和准确性。本文将详细阐述VMM的基本概念、应用和优势。

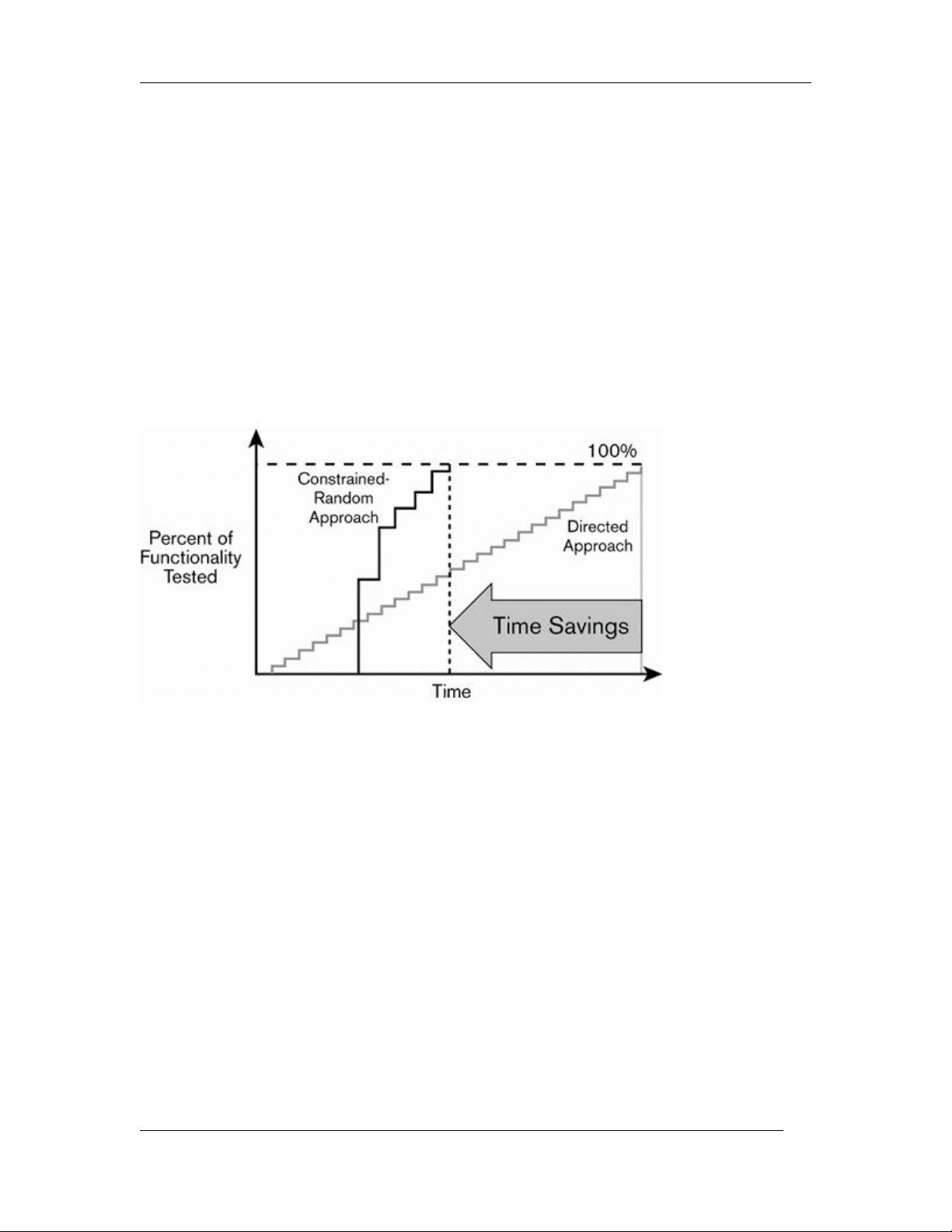

在第一部分,文章介绍了使用SystemVerilog进行复杂SoC验证的基础方法,涵盖了验证过程中所面临的挑战,如设计规模、功能复杂性等,并探讨了SystemVerilog的验证技术,包括约束随机仿真,这是现代验证中的关键组成部分,它能生成大量随机激励以充分覆盖设计的各种行为。此外,覆盖率驱动验证被强调,因为它是确保设计满足规范的关键指标,而断言则用于确保设计在各种条件下的正确性。

第二部分深入讨论了SystemVerilog验证方法学在RTL(寄存器传输级)验证中的应用,提出了分层测试平台结构。这种结构允许验证组件在不同层次上独立工作,增强了重用性和可维护性。文中还提到了自顶向下和自底向上的验证策略,前者从高层次开始验证,后者则从底层模块开始。结果检查、覆盖率驱动验证执行、形式分析工具的使用,以及如何生成可重用的验证知识产权(VIP)也是这一部分的重点。

第三部分转向系统级验证,探讨了SystemVerilog如何与SystemC协同工作,以实现硬件-软件协同验证。SystemC作为一个高级语言,常用于系统级模拟,与SystemVerilog的交互可以为实现完整的RTL到ESL(电子系统级)验证环境提供支持。

第四部分详细讨论了VMM方法学本身,包括验证策略和VMM库的使用。这些库提供了标准化的框架,帮助实现VMM方法学,例如XVC(eXtended Verification Component)管理器和软件验证工具。VMM方法学的广泛应用和认可,如Synopsys、ARM等公司的实践经验,以及相关书籍和教育课程的出现,都证明了其在验证领域的价值。

VMM for SystemVerilog是解决现代SoC验证问题的强大工具,通过提供可扩展、可重用的验证环境,显著提高了验证效率和成功率。对于任何从事SoC设计验证的团队来说,理解和应用VMM方法学都是极其重要的。"

2011-02-16 上传

2012-10-18 上传

2015-03-26 上传

2009-11-13 上传

2020-01-01 上传

2011-02-16 上传

2010-05-11 上传

2012-05-20 上传

sun_sun_sun_sun

- 粉丝: 0

- 资源: 1

最新资源

- PIEROutil:PIERO的AR客户端库(http

- terraform-courses

- bender:JIRA微管理助手

- phywcri,c语言曲线拟合源码下载,c语言

- PersonAttributeExt:人物属性提取

- 基于JAVA图书馆座位预约管理系统计算机毕业设计源码+数据库+lw文档+系统+部署

- poordub:可怜的人的PyDub

- system-simulation:使用 networkx python 库在图上模拟医院位置

- 4411513,socket源码c语言,c语言

- 52挂Q v1.3

- app-status

- srpagotest

- kettle的web版本,自己编译的war包,直接放到tomcat下运行,然后http://localhost:8080/web

- Ksdacllp-Backend:Ksdacllp后端

- chromedriver-linux64-V124.0.6367.91 稳定版

- php-pdf-filler