Quartus设计:3位循环码计时器与60s倒计时实现

需积分: 48 156 浏览量

更新于2024-08-11

2

收藏 240KB DOC 举报

本资源主要介绍了如何在Quartus II软件中实现两个与数字电子实验相关的项目:定时器设计和3位循环码计数器设计。

1. 定时器设计

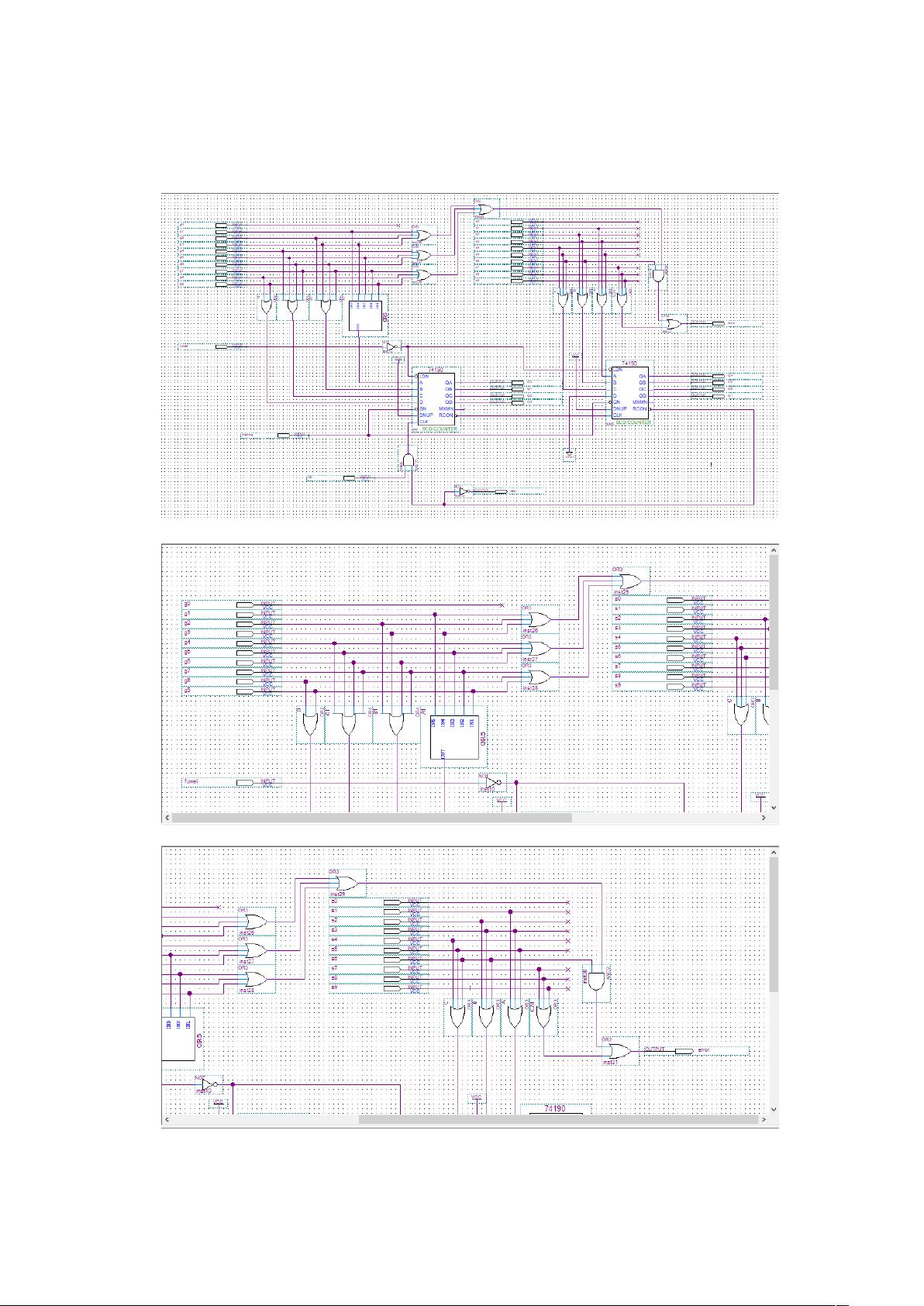

电路图展示了一个60秒以内可编程倒计时的定时器,它基于74190十进制减法计数器。该电路结构清晰,包括时钟(CLK)输入,暂停(PAUSE)输入,复位(RESET)输入,以及个位和十位输入。计时结束后,最下面的输出(end)变为高电平,而上方错误指示则在输入超过60时触发。电路工作原理是通过计数器逐位减去设定的时间,同时监控暂停信号来控制计时的暂停和重启。

仿真波形展示了32秒的计时过程,清晰地显示了计时器从开始到结束的整个过程,包括计数器状态的变化和最终的计时结束标志。

2. 3位循环码计数器设计

提供的Verilog代码定义了一个名为`xunhuanjishu`的模块,用于实现3位循环计数。计数器的工作原理基于组合逻辑,每当时钟脉冲(posedge clk)上升沿到来,如果`res`为高,计数器会重置为000。然后按照固定的模式000、001、011、010、110、111、101、100、000循环计数。`res`输入可以用来手动置零计数器的当前值。

仿真波形展示了计数器的运行过程,当`res`置1后,计数器按照预设的循环模式进行计数,每个计数周期对应一个三位循环码。

通过这些内容,学习者可以掌握如何在Quartus II环境下设计和实现数字定时器以及基本的循环计数器,这对于理解和应用数字逻辑设计至关重要。通过实际操作和理解这些电路原理,能够提升对数字电子和硬件设计的理解能力。

2047 浏览量

1130 浏览量

1144 浏览量

109 浏览量

182 浏览量

568 浏览量

篮球计时器fpga设计 verilog语言编写 支持quartus,modelsim,vivado设计 1.数码管显示每小节12分钟倒计时 2.数码管显示24s倒计时 3.数码管显示两队比分 4.按键

2025-01-09 上传

116 浏览量

m0_51955757

- 粉丝: 0

最新资源

- 深入解析ARM嵌入式Linux系统开发教程

- 精通JavaScript实例应用

- sndspec: 将声音文件转换为频谱图的工具

- 全技术栈蓝黄企业站模板(HTML源码+使用指南)

- OCaml实现蒙特卡罗模拟投资组合运行于网络工作者

- 实现TMS320F28069 LCD显示与可调PWM频率输出

- 《自动控制原理第三版》孙炳达课后答案解析

- 深入学习RHEL6下KVM虚拟化技术

- 基于混沌序列的Matlab数字图像加密技术详解

- NumMath开源软件:图形化数值计算与结果可视化

- 绿色大气个人摄影相册网站模板源码下载

- OpenOffice集成jar包:实现Word与PDF转换功能

- 雷达数字下变频MATLAB仿真技术研究

- PHP面向对象开发核心关键字深入解析

- Node.js中PostgreSQL咨询锁的实践与应用场景

- AIHelp WEB SDK代码示例及集成指南