SN75DP126

www.ti.com.cn

ZHCS794A –FEBRUARY 2012–REVISED MARCH 2012

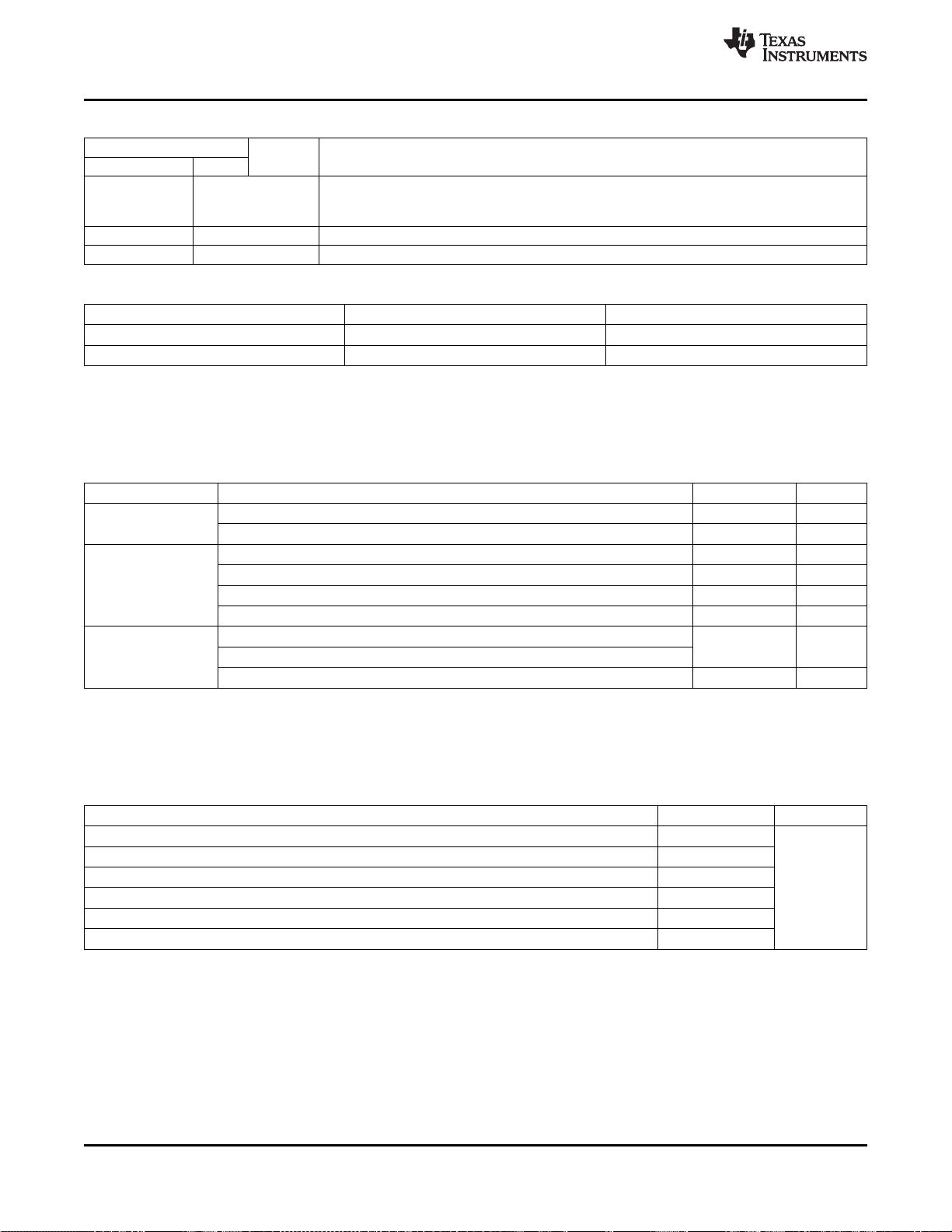

RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

V

CC

Supply voltage 3 3.3 3.6 V

V

DD

Digital core and Main Link supply voltage 1.0 1.05 1.2 V

T

A

Operating free-air temperature 0 85 °C

T

S

Storage temperature -65 150 °C

T

CASE

Case temperature 97.1 °C

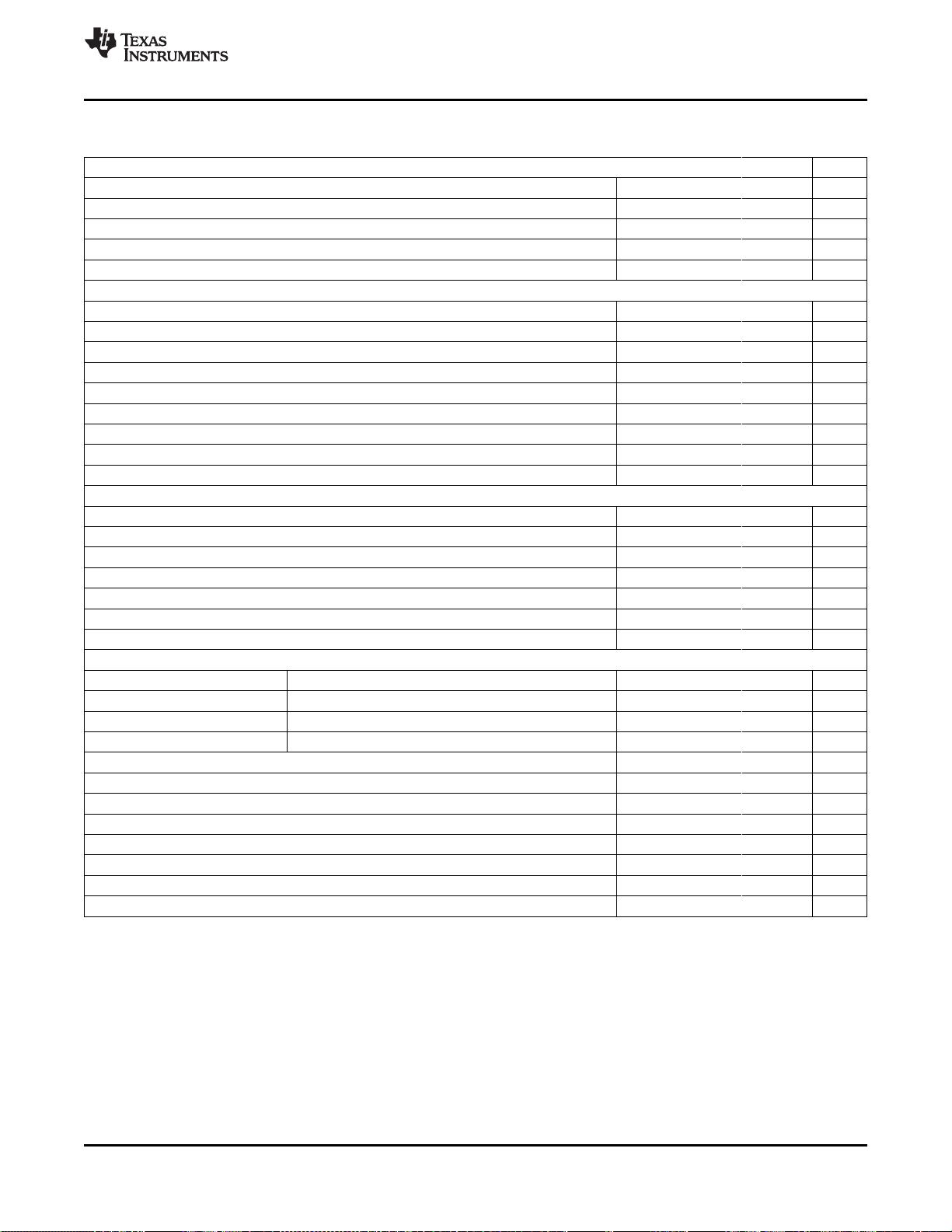

DP++ MAIN LINK TERMINALS

V

ID

Peak-to-peak input differential voltage; RBR, HBR, HBR2 0.3 1.40 Vpp

d

R(DP)

Data rate; DisplayPort sink 5.4 Gbps

d

R(HDMI)

Data rate; HDMI sink 3.4 Gbps

C

AC

AC coupling capacitance (each DP input and each DP output line) 75 200 nF

R

tdiff

Differential output termination resistance; DisplayPort sink and HDMI sink 80 100 120 Ω

V

Oterm

Output termination voltage (AC coupled) 0 2 V

t

SK(HBR2)

Intra-pair skew at the input at 5.4 Gbps 20 ps

t

SK(HBR)

Intra-pair skew at the input at 2.7 Gbps 100 ps

t

SK(RBR)

Intra-pair skew at the input at 1.62 Gbps 300 ps

AUX CHANNEL DATA TERMINALS

V

I-DC

DC Input Voltage, AUX_SRCp/n and AUX_SNKp/n (DP and TMDS modes) -0.5 3.6 V

V

ID

Differential input voltage amplitude (DP mode only) 300 1400 mV

PP

d

R(AUX)

Data rate (before Manchester encoding) 0.8 1 1.2 Mbps

d

R(FAUX)

Data rate Fast AUX (300ppm frequency tolerance) 720 Mbps

t

jccin_adj

Cycle-to-cycle AUX input jitter adjacent cycle (DP mode only) 0.05 UI

t

jccin

Cycle-to-cycle AUX input jitter within one cycle (DP mode only) 0.1 UI

C

AC

AUX AC coupling capacitance 75 200 nF

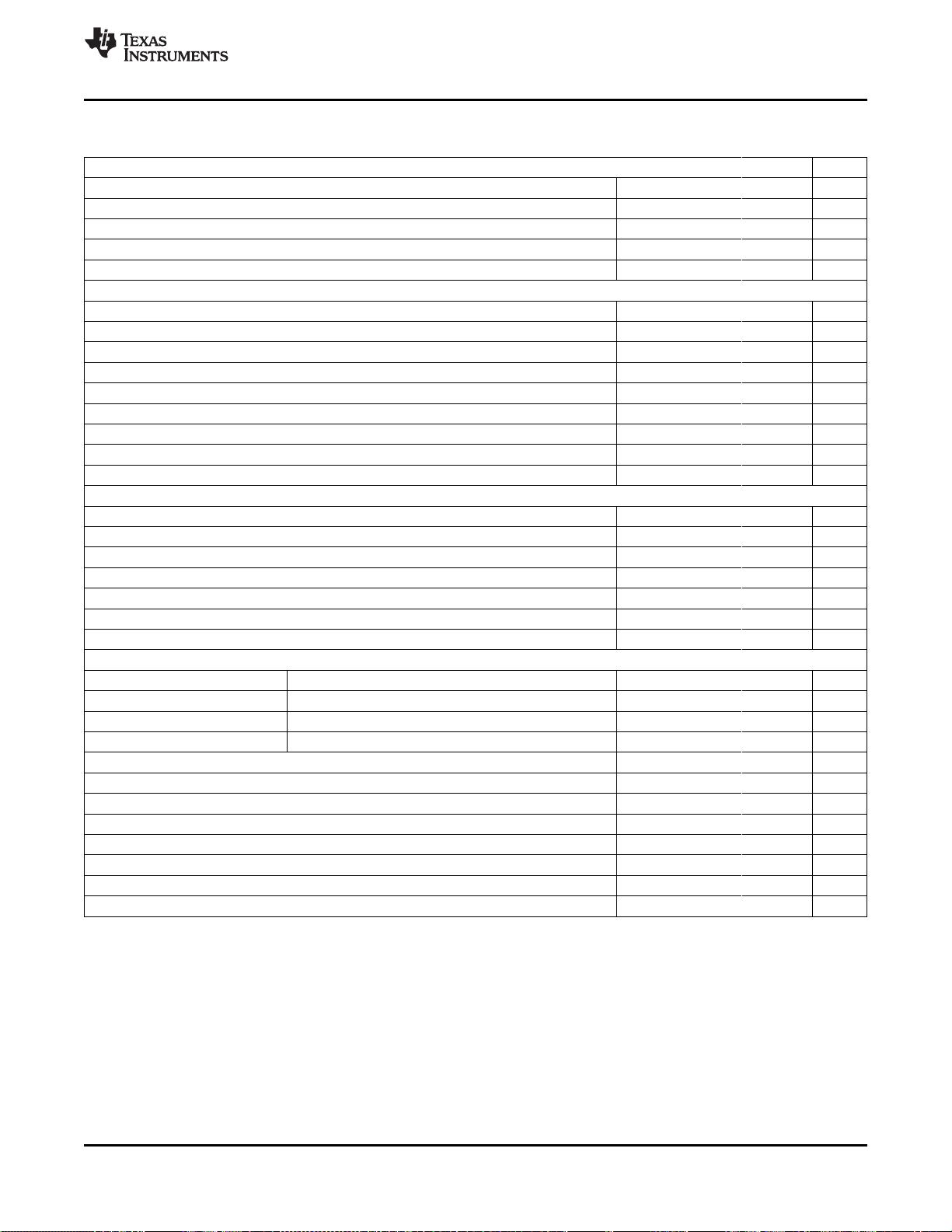

DDC, LOCAL I

2

C, AND CONTROL TERMINALS

V

I-DC

DC Input Voltage DP_HPD_SNK, TMDS_HPD_SNK, SCL/SDA_SNK –0.3 5.5 V

All other DDC, local I

2

C, and control terminals –0.3 3.6

V

IH

High-level input voltage SCL/SDA_SRC 2.1 V

All other DDC, Local I

2

C, and control terminals V

CC

–0.5

V

IL

Low-level input voltage

(1)

0.5 V

V

IM

Mid-level input voltage

(2)

V

CC

/2–0.3 V

CC

/2+0.3

d

R

Data rate 100 kbps

V

TH(EN)

EN input threshold voltage 280 800 mV

f

SCL

SCL clock frequency standard I

2

C mode 100 kHz

t

w(L)

SCL clock low period standard I

2

C mode 4.7 μs

t

w(H)

SCL clock high period standard I

2

C mode 4.0 μs

C

bus

Total capacitive load for each bus line (DDC and local I

2

C terminals) 400 pF

(1) V

IL

for SCL_SRC and SDA_SRC are listed in the AUX/DDC/I

2

C Electrical Characteristics Table.

(2) V

IM

is only applicable for 3-Level control pins.

Copyright © 2012, Texas Instruments Incorporated 9