"Xilinx UG906时序分析与改进方法详解"

需积分: 5 122 浏览量

更新于2023-12-29

1

收藏 11.96MB PDF 举报

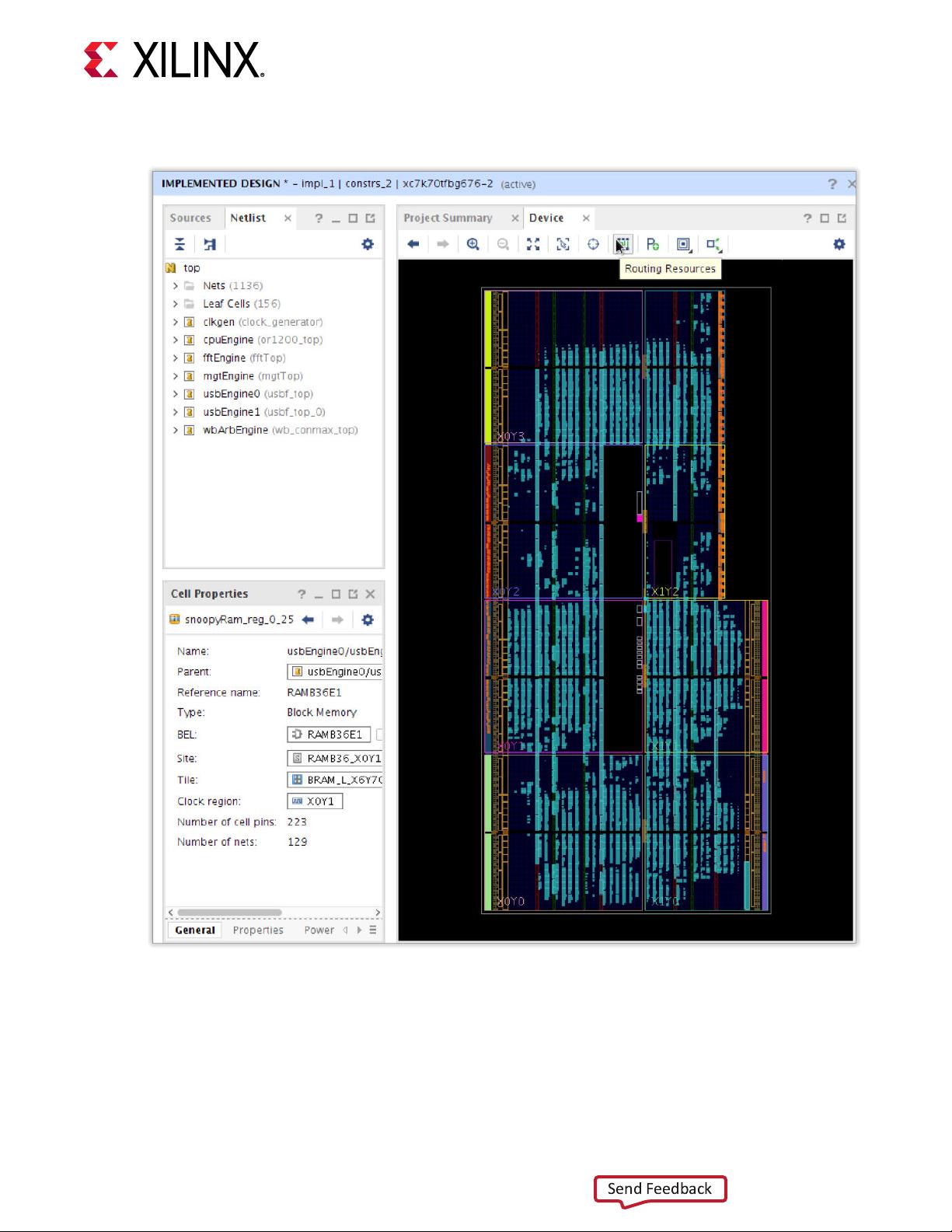

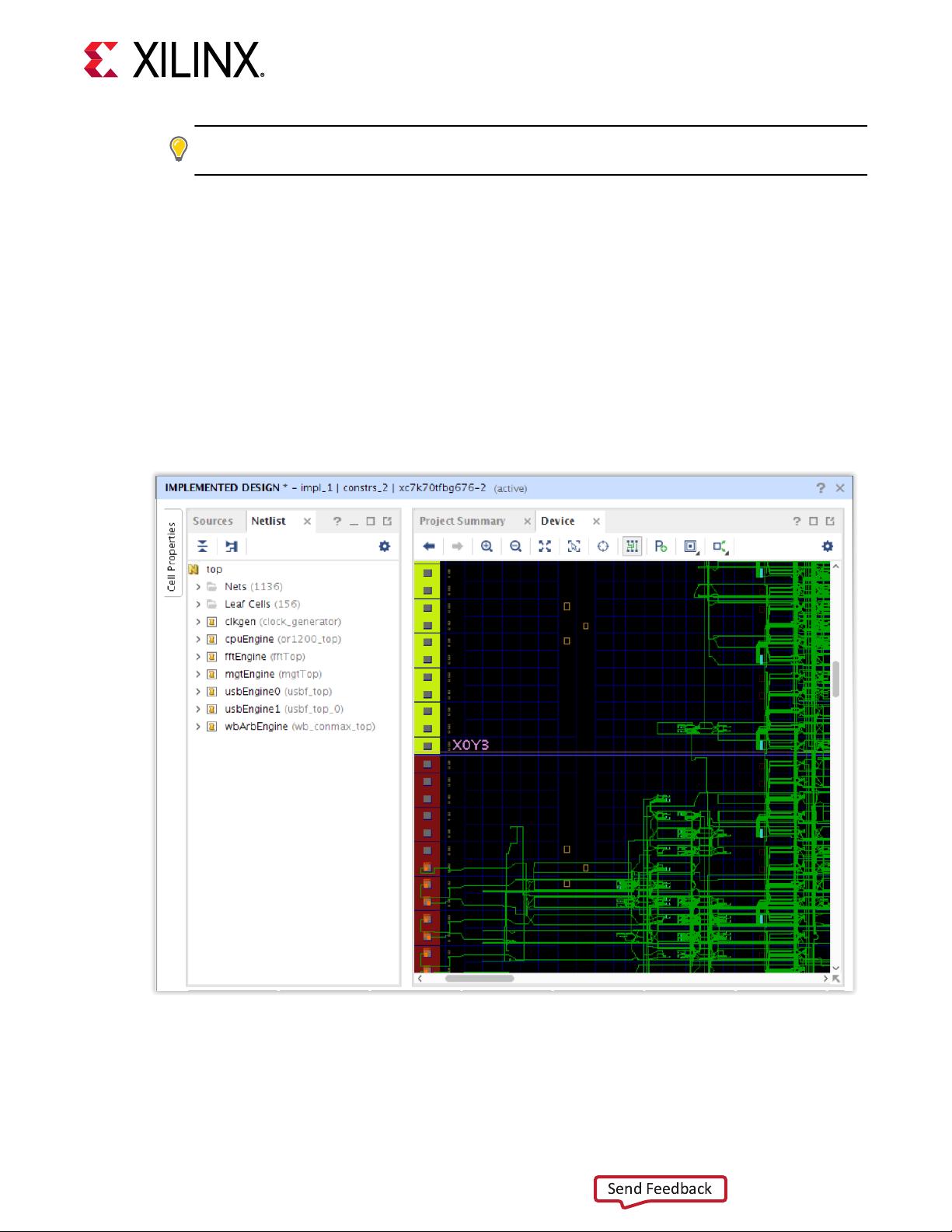

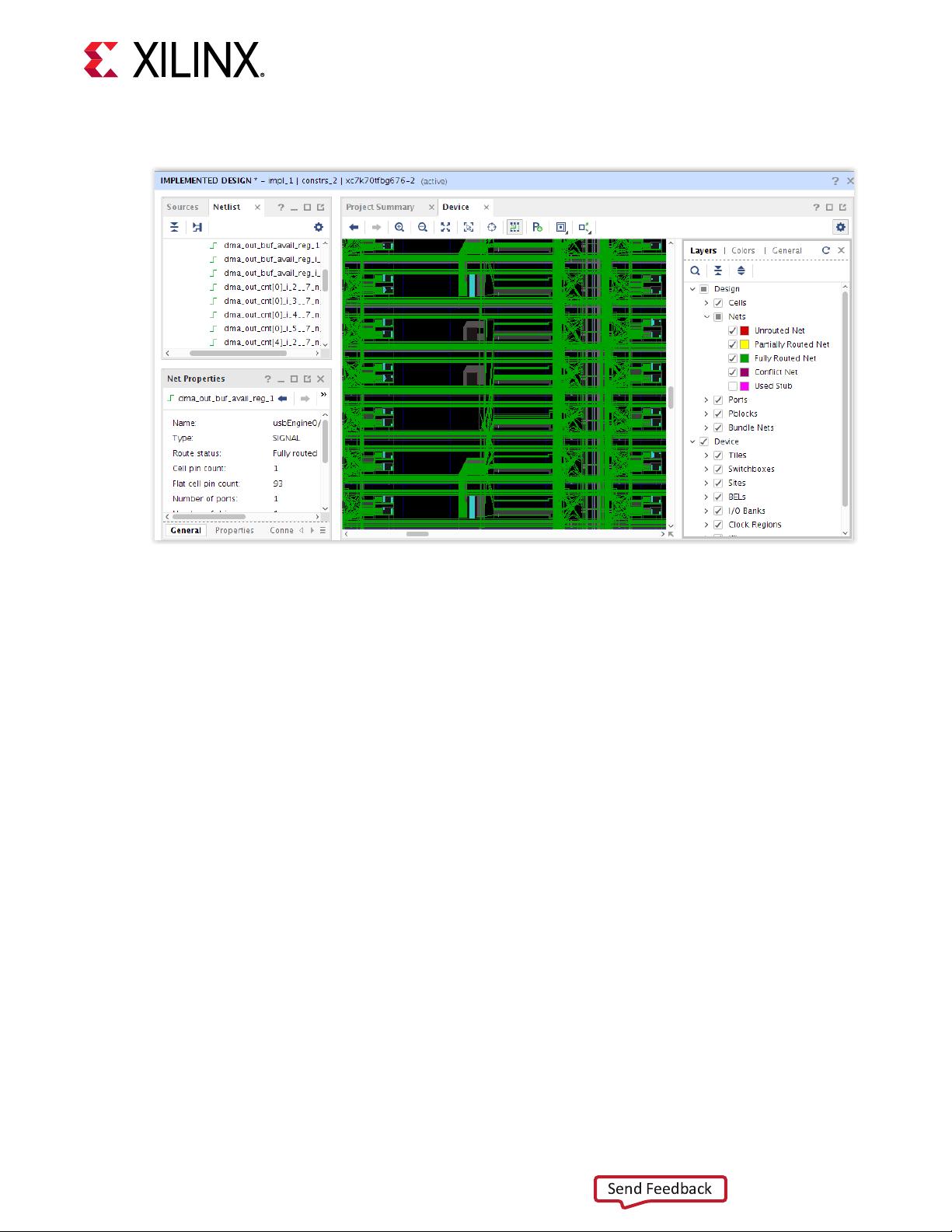

Xilinx UG906时序分析是一个重要的设计工具,本文档提供了关于如何使用 AMD Vivado Design Suite 来分析和改善设计的详细指南。其中包括了使用Vivado集成设计环境(IDE)来查看消息、设计网表和交叉探测的方法,以及方法论和DRC豁免的讨论。此外,该文档还介绍了分析时序报告的生成,包括所有网表、时序和设计收敛报告的生成方法。另外,文档还提供了智能设计运行、QoR建议和ML策略等方面的指导。

在Xilinx UG906时序分析中,用户可以借助Vivado集成设计环境(IDE)来查看消息、设计网表和进行交叉探测。通过IDE,用户可以轻松地浏览设计中的各种信息,并且可以进行实时的交叉探测,以便更好地理解设计中的各个部分。同时,该文档还探讨了方法论和DRC豁免,帮助用户了解如何在设计过程中遵循最佳实践,并且了解何时可以豁免一些设计规则检查。

此外,文档还介绍了分析时序报告的生成方法,包括生成所有网表、时序和设计收敛报告,这些报告对于设计分析和改进非常重要。用户可以通过这些报告来全面了解设计的时序特性,并且可以根据报告中的信息进行相应的优化和改进。

另外,文档还提供了智能设计运行、QoR建议和ML策略等方面的指导,帮助用户更好地理解如何利用Vivado Design Suite来提升设计的质量。智能设计运行、QoR建议和ML策略可以帮助用户自动化地优化设计,并且提供了一些建议和策略,以便更好地满足设计的要求。

总的来说,Xilinx UG906时序分析是一个非常重要的设计工具,而本文档提供了关于如何使用AMD Vivado Design Suite来分析和改善设计的详细指南。通过本文档,用户可以学习如何利用Vivado集成设计环境(IDE)来进行设计分析,以及了解方法论和DRC豁免的相关知识。此外,文档还介绍了分析时序报告的生成方法,以及如何利用智能设计运行、QoR建议和ML策略来提升设计的质量。通过这些内容,用户可以更好地掌握时序分析的方法和技巧,从而更好地改善设计并提升设计的质量。

197 浏览量

242 浏览量

2023-11-05 上传

2023-10-19 上传

115 浏览量

2024-06-23 上传

1272 浏览量