Quartus II 使用教程:从新建工程到Verilog HDL设计编译

需积分: 16 71 浏览量

更新于2024-09-09

收藏 1.29MB PDF 举报

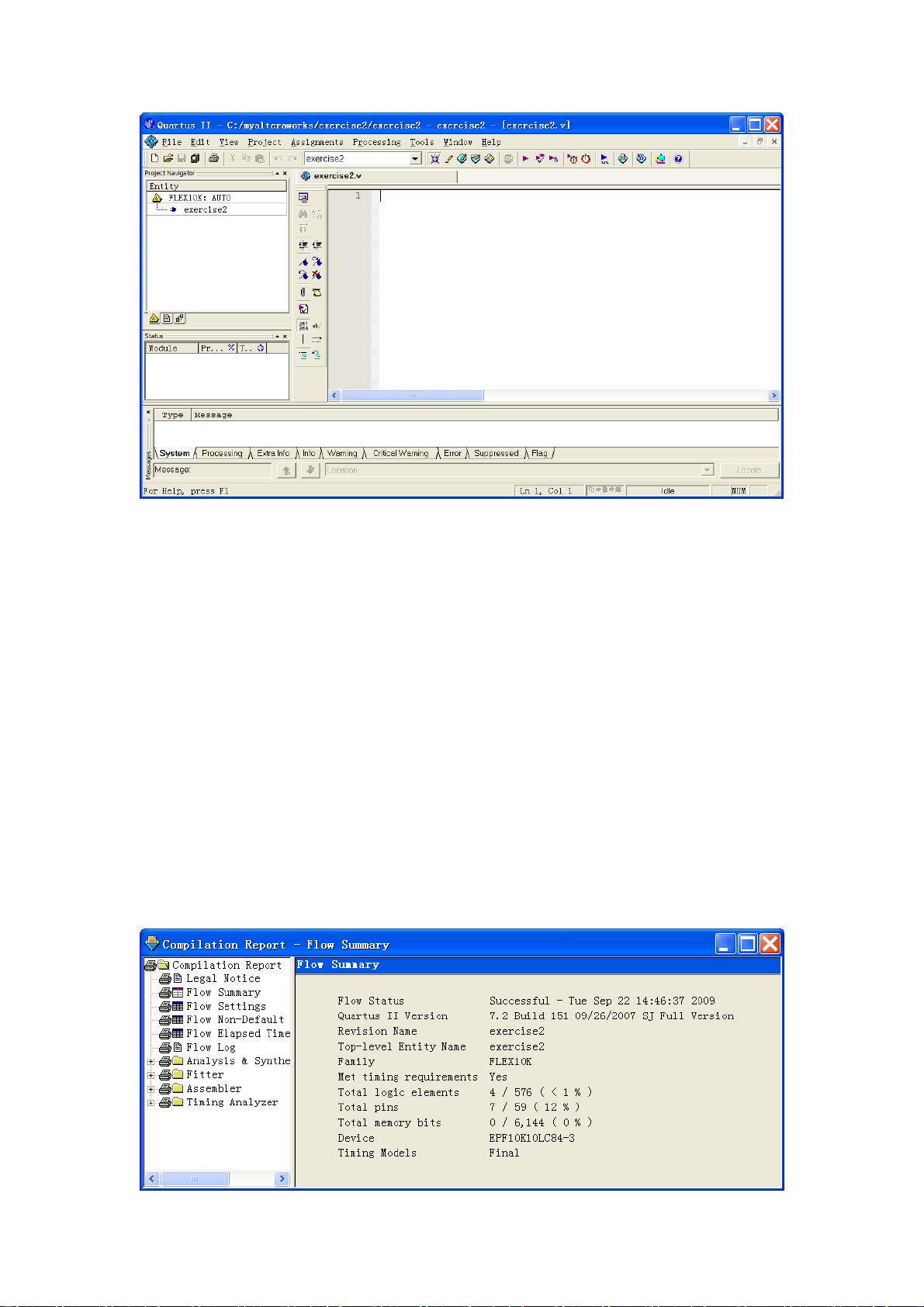

"Quartus II 是一款由Altera公司开发的用于FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)设计的集成开发环境。它提供了从设计输入、综合、仿真、布局布线到编程下载的全套工具链,使得用户能够高效地完成数字电路的设计工作。Quartus II 支持多种硬件描述语言(HDL),如VHDL和Verilog,以及Altera特有的Qsys系统级设计工具。在本资源中,我们将探讨如何使用Quartus II 进行基本的设计流程,包括新建工程、设置工程参数、设计输入、功能仿真以及布局布线等关键步骤。"

一、新建工程

创建一个新的工程是所有设计的起点。在Quartus II 中,你可以通过选择“File”菜单下的“New Project Wizard”来启动这个过程。在新建项目向导中,你可以设定项目名称、存储位置,以及选择项目所使用的器件系列。一旦项目创建完毕,可以通过“Assignments”菜单的“Settings”选项进一步细化工程的配置。

二、工程参数设置

1. 设定PLD器件:在“Settings”对话框的“Device”部分,你可以选择器件系列,例如FLEX10K系列,并可具体指定器件型号或者选择让Fitter自动选择最合适的器件以满足设计需求。

2. 用户库设置:在“User Library (Current Project)”选项中,可以添加或选择要使用的库,包括自定义库和第三方库,这有助于管理设计元素和模块。

三、设计输入

Quartus II 支持两种主要的HDL语言,VHDL和Verilog。对于Verilog HDL输入:

1. 使用“File”菜单的“New”命令创建新的Verilog文件。

2. 在出现的对话框中选择“Verilog HDL File”,并点击“OK”。

3. 文件命名后,可以在工作区中输入Verilog代码。例如,一个简单的加法器模块可以这样定义:

```verilog

module exercise2(input a, b, cin, output sum1, cout1, output reg sum2, cout2);

assign sum1 = a ^ b ^ cin;

assign cout1 = (a && b) || (a && cin) || (b && cin);

always @(*) begin

{cout2, sum2} = a + b + cin;

end

endmodule

```

四、设计编译

完成设计输入后,需要进行编译以检查语法错误和逻辑错误。通过选择“Processing”菜单下的“Compiler Tool”启动编译过程。编译过程中,Quartus II 会生成一份报告,列出设计中可能存在的问题,并提供解决问题的建议。

五、功能/时序仿真

在设计验证阶段,可以使用Quartus II 内置的ModelSim仿真器进行功能仿真。通过编写测试平台(Testbench)对设计模块进行激励,并观察其输出是否符合预期。这一步对于确保设计的正确性至关重要。

六、布局布线

编译无误后,下一步是布局布线。Quartus II 自动将逻辑设计映射到选定的FPGA器件上,优化逻辑资源分配并布线。布局布线的结果会在“Assignment Editor”的“Fit Results”中显示,包括利用率、速度等信息。

总结,Quartus II 提供了一个全面的平台,从设计输入到硬件实现,帮助工程师高效地完成FPGA/CPLD设计任务。通过理解并熟练掌握上述步骤,用户能够更好地利用Quartus II 实现复杂数字系统的开发。

2009-11-26 上传

2011-04-03 上传

2011-12-18 上传

2018-04-26 上传

zhix1n

- 粉丝: 0

- 资源: 4

最新资源

- MA82G5D16.zip

- memoryleakexample

- 简书练习代码Demo

- 华为服务器RH2288hv3 BIOS.zip

- 智能电源无线充电解决方案(原理图、PCB源文件、设计报告等)-电路方案

- composed-validations:有意义的Javascript验证库

- test-action-001

- baseJava

- 电子功用-基于多合一传感器的电缆线路在线监测系统

- react-component-boilerplate:React 组件样板。 使用 Karma 快速、持续地测试您的组件

- 密码学校_作业

- DebtCount

- QuickStack:前端Webapp和后端微服务模板,可以作为一个整体运行,也可以作为单独的Webapps微服务运行

- 基于NT0880 电梯完整解决方案(整个功能模块原理图、PCB源文件、视频演示)-电路方案

- Java进阶高手课-并发编程透彻理解

- Android实现3D图像显示源代码