"TI-TCAN4420.pdf: CAN收发器功能解析与控制逻辑详解"

67 浏览量

更新于2024-01-17

4

收藏 1.2MB PDF 举报

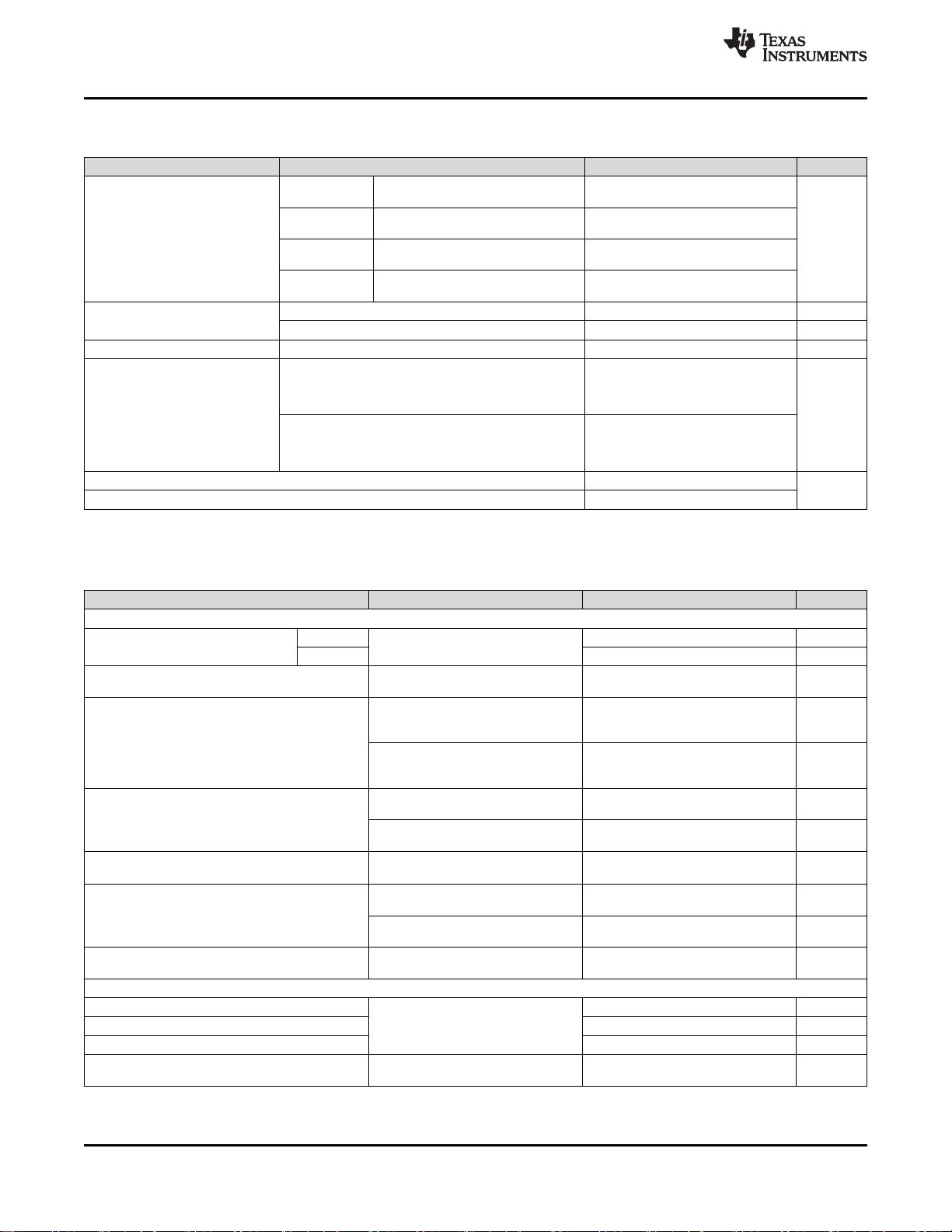

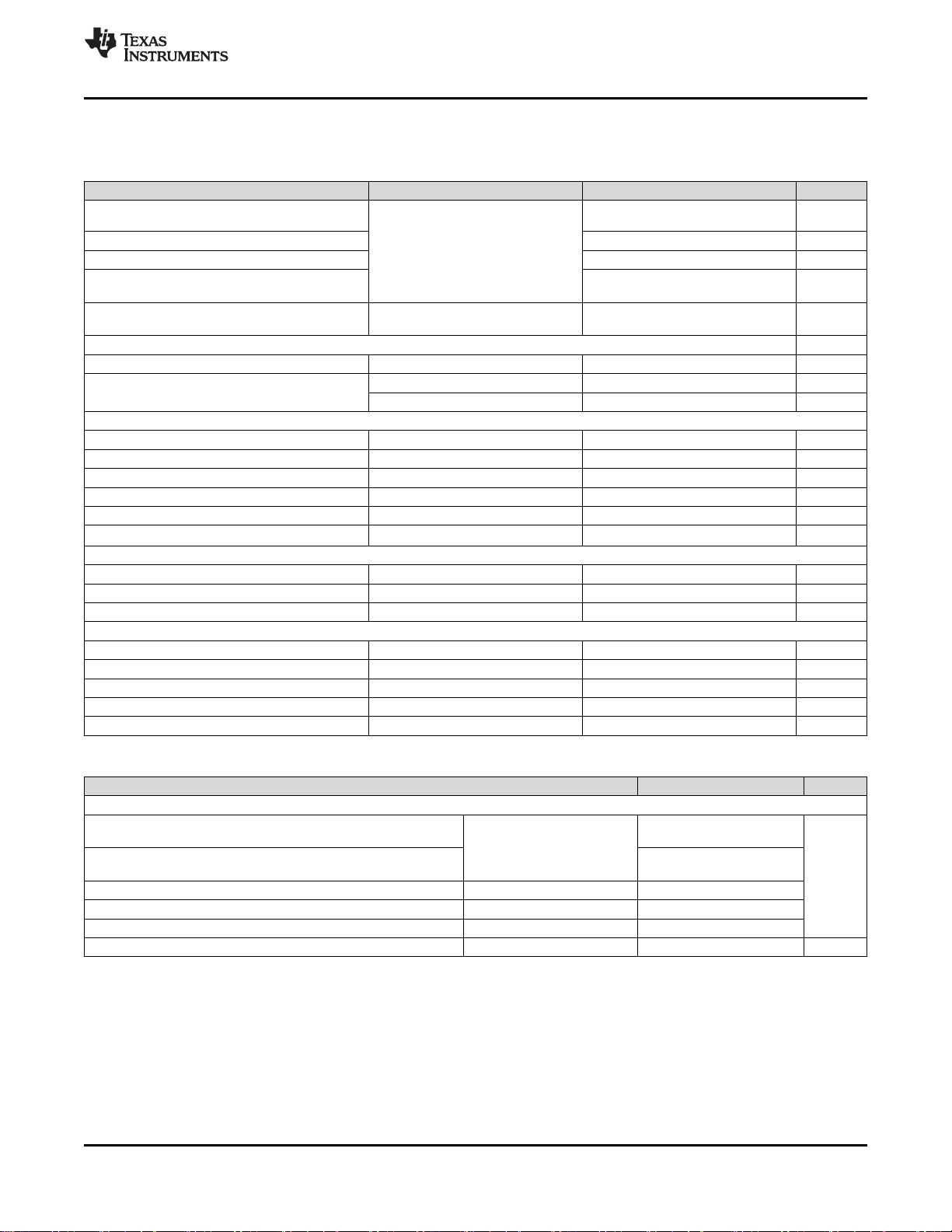

The TI-TCAN4420.pdf document provides detailed information on the CAN transceiver model TI-TCAN4420, which is a highly integrated device suitable for use in automotive and industrial applications. The transceiver features include TXD, RXD, VCC, GND, Polarity Control, SWCAN, HCAN, Dominant Time Out, OverTemp. DRIVER, UnderVoltage Mode and Control Logic, Bias Unit Logic Output, and VIO, as well as copyright information indicating the document is the property of Texas Instruments Incorporated. The document is part of the ProductFolder, which contains comprehensive information about the TI-TCAN4420 transceiver, including the option to OrderNow, access to TechnicalDocuments, and tools for further support and development. The detailed content of the document provides engineers and designers with the necessary information to understand, integrate, and utilize the TI-TCAN4420 transceiver in their systems, ensuring reliable and efficient performance in CAN communication applications.

286 浏览量

261 浏览量

2022-11-14 上传

2022-12-16 上传

2022-12-16 上传

2022-12-16 上传

2022-12-16 上传

122 浏览量

119 浏览量

不觉明了

- 粉丝: 8301

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程