DDR3技术详解:从JESD79-3标准到实战应用

版权申诉

"这份文档是关于JESD79-3 DDR3标准的深度解析,旨在帮助读者理解和掌握DDR3内存技术。文档作者具有丰富的行业经验和专业知识,对JEDEC标准有深入的理解,并提供答疑和退款保障。文档内容涵盖DDR3与DDR2的区别、DDR3的不同版本(如DDR3L和DDR3U)、SDRAM的同步特性、同步与异步内存的对比、DDR3中的新特性如RESET引脚和ZQ校准等。同时,文档还涉及DDR3的相关问题,如Write Leveling、Read Leveling、Prefetch机制以及DRAM尺寸和页大小的计算等。此外,标签显示文档还将对比DDR3与DDR4、LPDDR3、LPDDR4以及DDR5等其他内存类型。"

DDR3内存技术是计算机系统中重要的组成部分,它在DDR2的基础上进行了多项改进,以提高性能和能效。DDR3标准支持的频率范围从512Mb到8Gb,同时提供了低功耗版本DDR3L(1.35V)和超低压版本DDR3U(1.25V)。SDRAM的“S”代表同步,意味着其操作频率与CPU外频同步,确保高效的内存访问。与异步内存不同,同步内存能够在同一时钟周期内完成读写操作,提高了系统的整体响应速度。

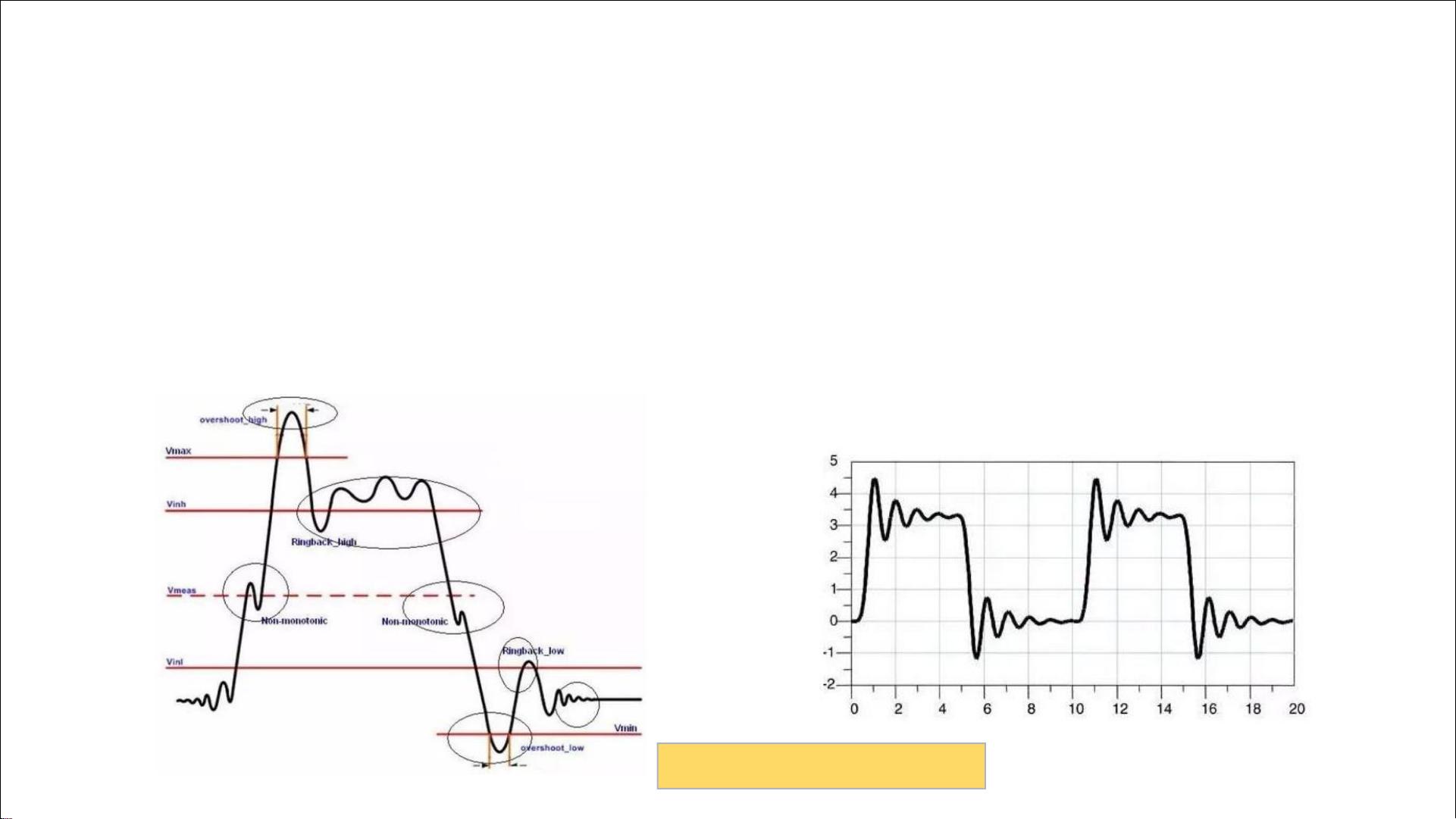

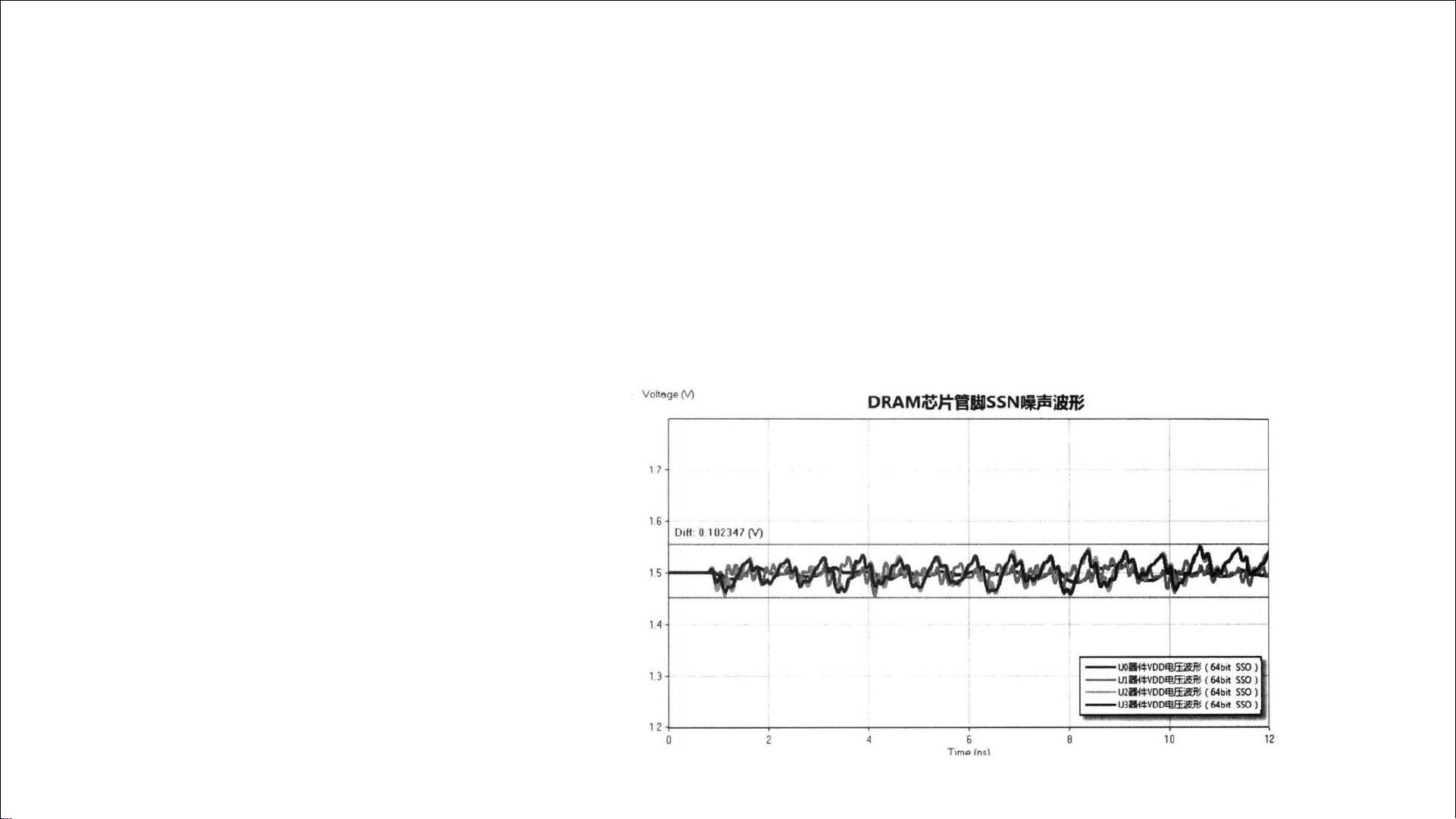

DDR3相对于DDR2的一个显著变化是引入了RESET引脚,简化了内存的复位操作,无需逐个控制寄存器设置,降低了系统复杂性。ZQ引脚则用于进行终端电阻(ZQ)校准,保证数据总线的信号完整性,这对于高速数据传输尤其关键。

Write Leveling和Read Leveling是DDR3中用于优化信号同步的技术。Write Leveling确保数据在正确的时间点被写入内存,而Read Leveling则调整读取时钟以匹配数据输出的边缘,这些技术提升了数据传输的精度。Prefetch机制则是DDR内存提高带宽的策略之一,它预取一定数量的数据,以减少等待时间,提高数据吞吐量。

DRAM的尺寸和页大小计算通常涉及到DRAM阵列的组织结构和内部bank的设计。MRS(Mode Register Set)命令用于设置DRAM的工作模式,但与之相反,MRR(Mode Register Read)在DDR3中并不存在,可能是因为其他命令或机制已经包含了类似的功能。

文档还讨论了BIOS如何识别不同类型的DIMM,例如DDR3和DDR4,这涉及到DIMM上的SPD(Serial Presence Detect)信息。XMP(Extreme Memory Profile)是Intel推出的一种内存超频标准,允许用户轻松地提高内存的性能。

这份文档深入浅出地介绍了DDR3内存技术的各个方面,对于开发者、硬件爱好者和系统工程师来说,是理解DDR3内存工作原理和特性的宝贵资源。

2204 浏览量

620 浏览量

2069 浏览量

774 浏览量

3828 浏览量

505 浏览量

1346 浏览量