ARM存储系统:协处理器CP15在嵌入式系统中的角色

105 浏览量

更新于2024-09-01

收藏 229KB PDF 举报

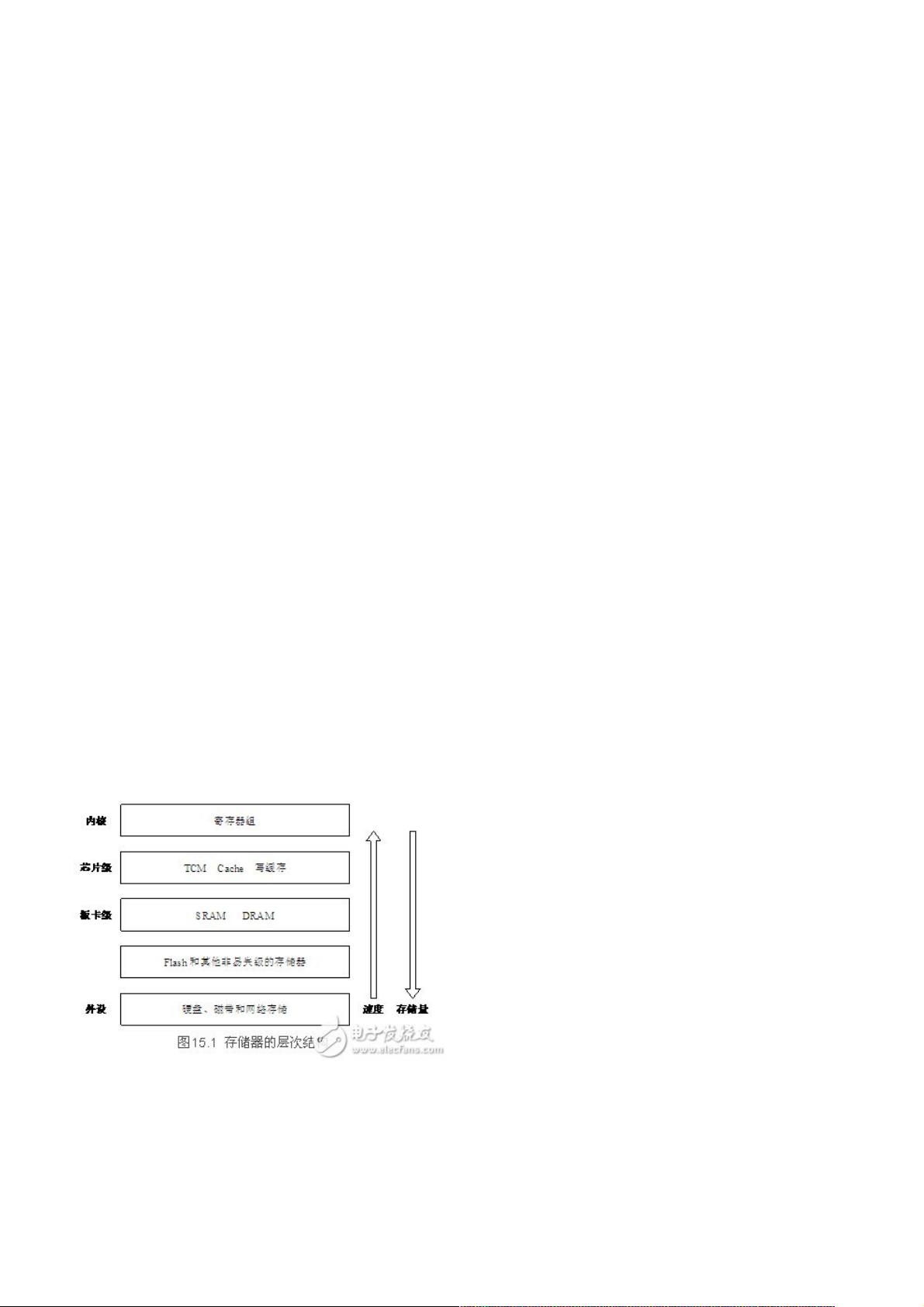

"ARM存储系统具有高度灵活性,适应各种嵌入式应用需求,通过平板式地址映射或更复杂技术实现。协处理器CP15在其中扮演关键角色,用于管理存储系统,包括Caches、虚拟内存映射、存储保护和I/O映射。ARM存储体系由多级构成,包括寄存器、高速缓存、主内存等,通过CP15实现高效管理和优化性能。"

在ARM架构中,存储器系统的设计至关重要,因为它直接影响到系统的性能和效率。协处理器CP15是这个系统中的一个核心组件,它负责处理与存储相关的高级控制任务。CP15不仅管理Cache,还涉及虚拟内存映射、存储保护和I/O操作的映射,确保不同存储器件的正确交互和数据一致性。

首先,让我们来看看Cache技术。Cache是存储系统中的一种高速缓冲,用于存放最近频繁访问的数据,以减少处理器访问较慢的主内存的次数,从而提升系统性能。ARM处理器通常有L1和L2 Cache,它们分别位于CPU核心附近,提供快速数据存取。CP15负责控制Cache的状态,包括启用、禁用、清除和替换策略。

其次,虚拟内存和地址映射对于嵌入式系统来说是非常关键的功能。虚拟内存允许程序在较大的地址空间中运行,即使实际可用的物理内存较小。通过页表,CP15实现虚拟地址到物理地址的转换,使得程序可以独立于物理内存布局运行。此外,通过内存映射,可以动态调整程序的运行位置,例如,启动时在ROM/FLASH中运行初始化代码,然后将运行负载转移到速度更快的SDRAM中。

存储保护机制是另一个重要的安全特性。CP15可以设置访问权限和区域,防止未经授权的访问,确保系统稳定性和数据安全。这对于多任务操作系统或者安全敏感的应用来说尤其重要。

最后,I/O操作在简单存储系统中直接映射到物理地址,但在有Cache和writebuffer的系统中,需要特殊处理以确保正确执行。CP15提供了这样的机制,使得I/O设备的访问能够适应高速缓存的存在,避免数据同步问题。

ARM的存储器层次结构从寄存器开始,其次是高速缓存(如L1和L2 Cache),然后是主内存(如DRAM或SRAM),最后可能是外部存储设备如Flash或ROM。每个层次都有其独特的访问速度和容量,CP15通过智能管理这些层次,优化数据流动,提升系统整体性能。

ARM存储系统通过灵活的地址映射机制和CP15的精细控制,实现了高效、安全和适应性强的嵌入式系统设计。无论是对嵌入式开发人员还是系统架构师,理解CP15的作用及其在存储管理中的功能都是至关重要的。

2018-05-08 上传

2011-11-11 上传

2010-10-06 上传

2010-05-15 上传

2022-07-07 上传

点击了解资源详情

weixin_38530202

- 粉丝: 2

- 资源: 876

最新资源

- BottleJS快速入门:演示JavaScript依赖注入优势

- vConsole插件使用教程:输出与复制日志文件

- Node.js v12.7.0版本发布 - 适合高性能Web服务器与网络应用

- Android中实现图片的双指和双击缩放功能

- Anum Pinki英语至乌尔都语开源词典:23000词汇会话

- 三菱电机SLIMDIP智能功率模块在变频洗衣机的应用分析

- 用JavaScript实现的剪刀石头布游戏指南

- Node.js v12.22.1版发布 - 跨平台JavaScript环境新选择

- Infix修复发布:探索新的中缀处理方式

- 罕见疾病酶替代疗法药物非临床研究指导原则报告

- Node.js v10.20.0 版本发布,性能卓越的服务器端JavaScript

- hap-java-client:Java实现的HAP客户端库解析

- Shreyas Satish的GitHub博客自动化静态站点技术解析

- vtomole个人博客网站建设与维护经验分享

- MEAN.JS全栈解决方案:打造MongoDB、Express、AngularJS和Node.js应用

- 东南大学网络空间安全学院复试代码解析