时序电路探析:从RS锁存器到D触发器

需积分: 0 13 浏览量

更新于2024-08-05

收藏 587KB PDF 举报

"该资源主要讲述了触发器和锁存器的基础知识,重点涵盖了RS锁存器、时钟触发的RS锁存器以及D锁存器的概念和工作原理。实验旨在通过学习加深对时序电路的理解,并通过Verilog语言实践阻塞赋值和非阻塞赋值的差异。"

在数字电路设计中,触发器和锁存器是构建时序逻辑电路的核心组件。它们具有存储数据的能力,并在特定条件下更新输出。本实验主要探讨了三种基本类型的锁存器和触发器:RS锁存器、时钟触发的RS锁存器以及D锁存器。

RS锁存器是最基础的类型,由与非门构成,具有Set(S)和Reset(R)两个输入端。RS锁存器的输出Q和非Q(Q')受到S和R的控制。当S为0且R为1时,锁存器置1(Q=1,Q'=0);当S为1且R为0时,锁存器置0(Q=0,Q'=1)。然而,当S和R都为0时,RS锁存器处于不定状态,这是不允许的。为解决这个问题,引入了时钟信号,形成了时钟触发的RS锁存器。这种改进版的锁存器在时钟信号(Clk)为0时保持当前状态,而在时钟上升沿(Clk=1)时根据S和R的值改变输出。

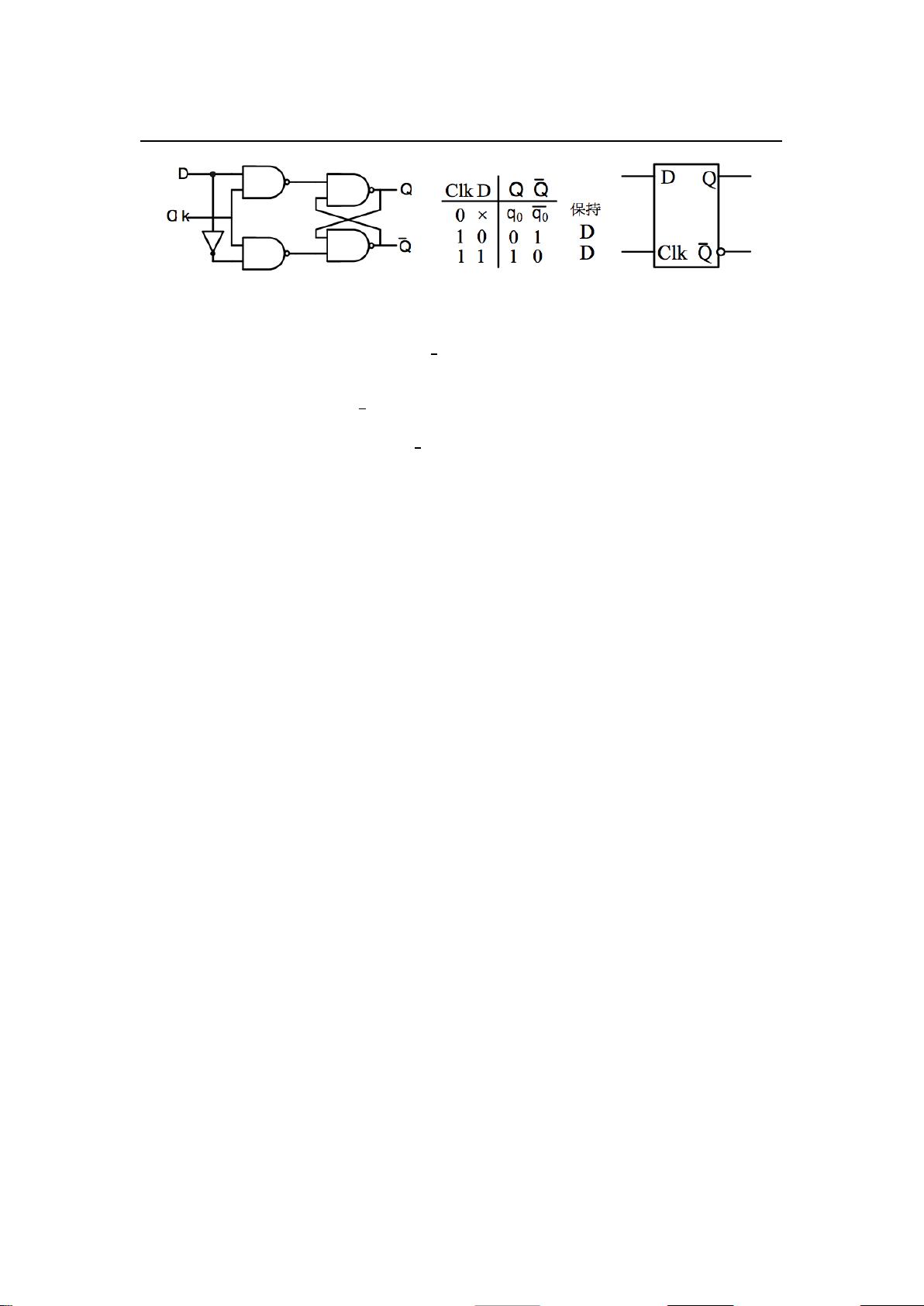

D锁存器(Data latch)是另一种重要的锁存器,它消除了RS锁存器的无效状态。D锁存器只有一个数据输入D和一个时钟输入Clk。在时钟信号为0时,D锁存器保持当前输出;当时钟信号变为1时,输出瞬间更新为D的值。这样,D锁存器确保在时钟边沿触发时数据的稳定传输,避免了无效状态。

在FPGA开发中,D触发器是最常用的时序逻辑单元,因为它们能够简单高效地存储和传输数据。理解RS锁存器和D锁存器的工作原理对理解和设计复杂的时序电路至关重要。实验还强调了通过Verilog语言进行时序电路仿真的方法,特别是阻塞赋值( Blocking assignment)和非阻塞赋值(Non-blocking assignment)的区别,这两者在描述时序逻辑行为时有着显著的不同。

这个实验旨在通过理论讲解和实际操作,帮助学习者掌握锁存器和触发器的工作原理,提升他们分析和设计时序电路的能力,为后续的FPGA项目开发打下坚实基础。

567 浏览量

112 浏览量

点击了解资源详情

387 浏览量

319 浏览量

353 浏览量

333 浏览量

521 浏览量

521 浏览量

八位数花园

- 粉丝: 865

- 资源: 281

最新资源

- windows+onlyoffice部署.zip

- claudiusvhds:Claudiu的VHD具有所有旧Windows操作系统(1.x-2000)

- DialGuageReader

- relaxation-labeling:一种基于最初的模糊身份标记对象的算法,基于“放松标记过程的基础”(Hummel 1983)

- matlab的slam代码-Navigation-module:具有高级规划器、低级控制器和EKFSLAM的导航模块

- revolver:少量分割

- ARM体系结构及编程 实验三 定时器中断实验

- 某汽车制造厂企业文化手册

- VacayCamp

- 电信设备-基于复眼透镜的摄像头、成像方法及移动终端.zip

- geoserver-2.16-RC-bin.zip

- aspnetcore电子商务

- Pollution-check-arduino:使用arduino测量污染并将数据存储在sd卡中或通过蓝牙传输数据

- mServices:龙卷风

- java飞机游戏.zip

- VB画图程序源码【课程设计】