FPGA嵌入式块SRAM设计详解与高速优化

107 浏览量

更新于2024-09-01

收藏 280KB PDF 举报

嵌入式块SRAM在FPGA中的设计是电子系统集成中的关键组成部分,特别是在逻辑芯片中,因其灵活性和成本效益而受到青睐。本文主要探讨的是如何在Xilinx公司的FPGA架构中实现高效的嵌入式块SRAM设计,特别是针对小型和高速存储需求的应用。

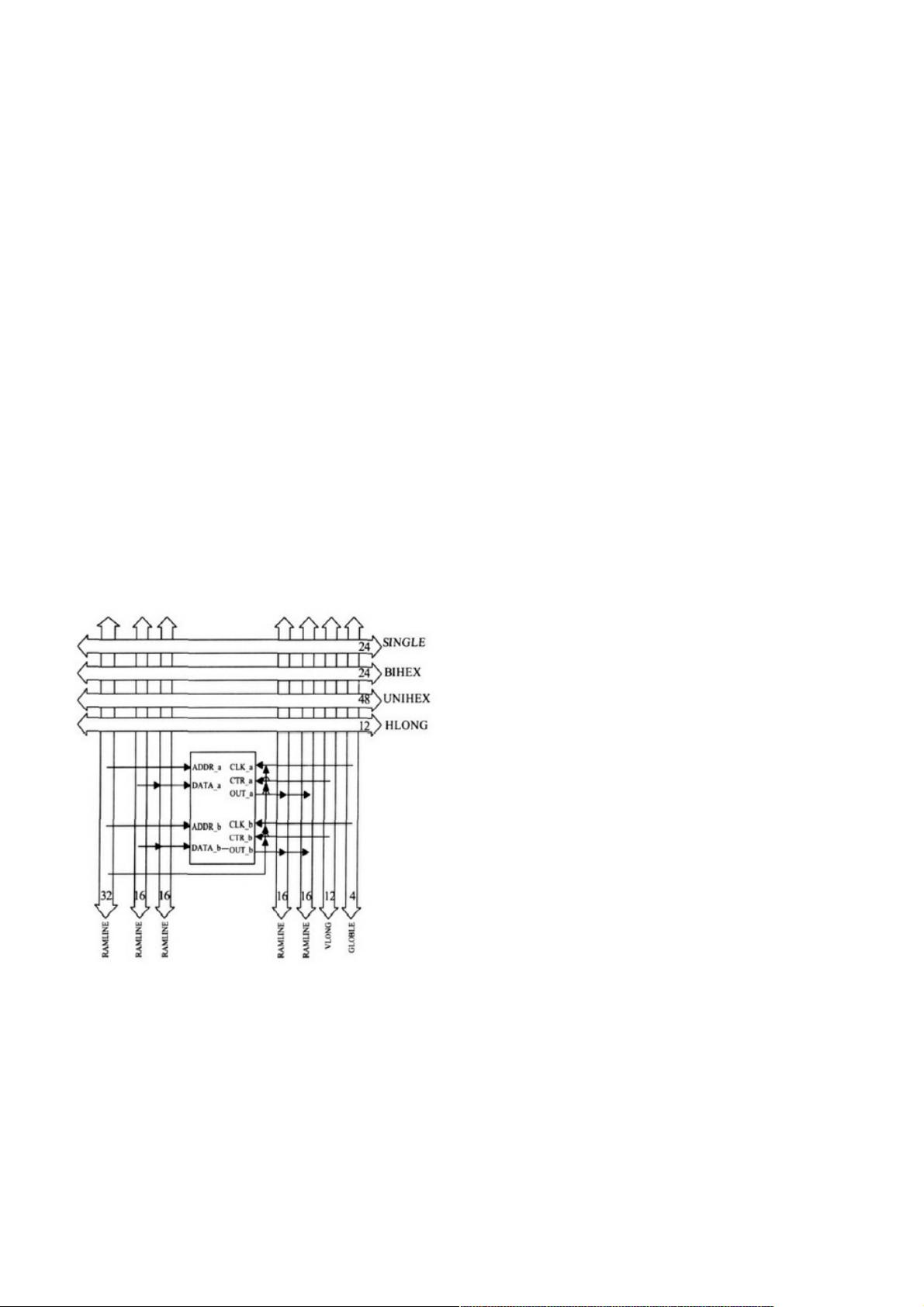

首先,文章从嵌入式SRAM的通用价值入手,指出在逻辑工艺兼容性方面,标准的6T单元SRAM是常见的选择,尤其对于小于2Mb的存储应用,嵌入式SRAM提供了经济性和性能的双重优势。Xilinx FPGA的架构包含多种组件,如配置存储器、可编程I/O、CLB(可编程逻辑单元)、BRAM(块存储器)以及数字时钟管理模块,其中分布式RAM位于CLB内,每个CLB内的SRAM具有16位宽。

为了满足现代数字系统对高速存储的需求,文章重点介绍了BRAM的块划分策略。通过将BRAM划分为多个独立的部分,可以降低位线和字线上的负载电容,从而加快读取速度。每个BRAM块都有自己的译码电路、敏感放大器和数据通道,实现了并行操作,显著提高了读取性能。

BRAM与FPGA布线资源的接口设计至关重要。每个BRAM块连接着RAMLINE、VLONG和GLOBAL线路,其中RAMLINE用于地址和控制信号的传输,而GLOBLE用于提供稳定的时钟信号。VLONG线则用于WE、ENA和RST等控制信号的传输。通过可编程开关矩阵PSM,信号可以在不同BRAM之间灵活路由,确保数据流的高效传输。

此外,文章还提到了相邻BRAM之间的RAMLINE连接,可能需要三态门来防止信号冲突,确保数据的准确传输。这种设计充分考虑了信号完整性问题,并强调了在有限的硬件资源下优化性能的重要性。

基于FPGA的嵌入式块SRAM设计是一个涉及硬件架构、布线策略和性能优化的复杂过程。通过细致的规划和实现,设计师可以利用FPGA的灵活性为系统提供高性能、低延迟的存储解决方案,满足不断增长的嵌入式系统对存储需求的挑战。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-08-07 上传

2020-10-23 上传

2019-09-05 上传

2020-10-23 上传

2021-07-13 上传

2020-11-03 上传

weixin_38703626

- 粉丝: 3

- 资源: 974

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍