Chipscope教程:从RTL设计到逻辑分析仪生成

需积分: 10 55 浏览量

更新于2024-07-26

收藏 437KB PDF 举报

"Chipscope 简明教程是一份指导如何使用Chipscope的PDF文档,由stevechou@21cn.com编写并发布在www.edaking.com。教程涵盖了从设置操作环境到实现RTL设计仿真以及逻辑分析仪的创建,主要针对使用Modelsim5.8进行仿真,Synplifypro7.5.1进行综合,ISE6.2进行布局,以及Chipscope6.2进行分析的流程。"

在本文档中,Chipscope被介绍为一种用于FPGA(Field-Programmable Gate Array)开发中的调试工具,它能够帮助工程师在硬件级别上观察和分析设计的运行情况。Chipscope提供了两种逻辑分析仪的产生方法:CoreGenerator和CoreInserter。

CoreInserter的方法涉及到以下步骤:

1. 将RTL设计综合成Netlist。

2. 使用CoreInserter插入逻辑分析仪。

3. 进行布局和布线。

4. 生成bit文件以下载验证。

相比之下,CoreGenerator的方法包括:

1. 直接调用CoreGenerator生成逻辑分析仪的Netlist。

2. 修改RTL设计,插入逻辑分析仪相关的代码。

3. 进行布局和布线。

4. 生成bit文件进行下载验证。

教程指出,由于CoreInserter需要在网表中搜索信号,相比修改RTL可能更为复杂,每次修改后还需要重新插入逻辑分析仪,因此教程选择了使用CoreGenerator流程,因为它允许在修改RTL后只需重新进行综合、布局和布线。

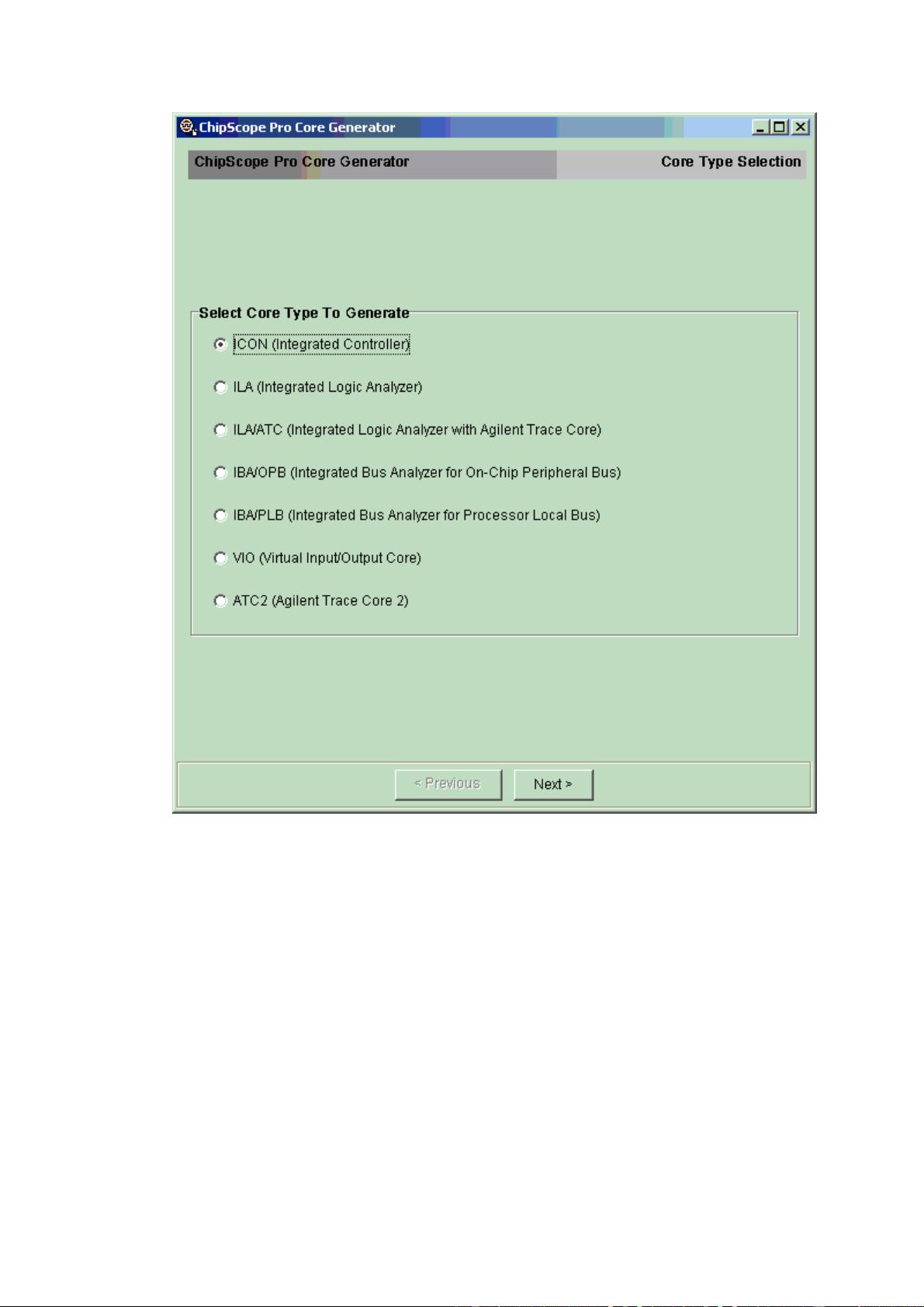

在使用CoreGenerator的步骤中,用户需要:

1. 打开ChipScopePro6.2的CoreGenerator。

2. 选择集成控制器(ICON)的产生。

3. 设置输出目录和设备家族。

4. 选择语言和综合工具。

5. 生成集成控制器。

6. 回到主菜单,选择ILA(集成逻辑分析仪)。

7. 设置输出目录、设备家族和采样时钟边缘。

8. 定义触发宽度和采样深度。

9. 选择数据端口与触发端口相同,并配置采样深度和所需的BlockRAM数量。

10. 选择语言和综合工具。

11. 最后,生成集成逻辑分析仪的核心。

通过这个教程,学习者可以掌握如何在FPGA设计流程中有效地使用Chipscope来调试和验证自己的设计,从而提高开发效率和设计质量。

点击了解资源详情

点击了解资源详情

200 浏览量

2009-08-19 上传

337 浏览量

153 浏览量

489 浏览量

109 浏览量

139 浏览量

huang_huang_0

- 粉丝: 0

最新资源

- HaneWin DHCP Server 3.0.34:全面支持DHCP/BOOTP的服务器软件

- 深度解析Spring 3.x企业级开发实战技巧

- Android平台录音上传下载与服务端交互完整教程

- Java教室预约系统:刷卡签到与角色管理

- 张金玉的个人简历网站设计与实现

- jiujie:探索Android项目的基础框架与开发工具

- 提升XP系统性能:4G内存支持插件详解

- 自托管笔记应用Notes:轻松跟踪与搜索笔记

- FPGA与SDRAM交互技术:详解读写操作及代码分享

- 掌握MAC加密算法,保障银行卡交易安全

- 深入理解MyBatis-Plus框架学习指南

- React-MapboxGLJS封装:打造WebGL矢量地图库

- 开源LibppGam库:质子-伽马射线截面函数参数化实现

- Wa的简单画廊应用程序:Wagtail扩展的图片库管理

- 全面支持Win7/Win8的MAC地址修改工具

- 木石百度图片采集器:深度采集与预览功能