VHDL实现:4位全加器设计与溢出检测

需积分: 3 4 浏览量

更新于2024-08-05

收藏 209KB DOCX 举报

"这篇文档是关于使用VHDL设计一个4位全加器的大学数电实验报告。设计目标是创建一个能处理4位二进制数加法的全加器,包括进位检测功能。设计过程中采用了4个1位全加器串联,并通过VHDL编程实现。"

在数字电子学领域,全加器是一种基本的数字逻辑电路,它不仅计算两个二进制数的和,还考虑了进位(carry)的影响。在这个实验中,设计者采用VHDL语言构建了一个4位全加器,用于实现两个4位二进制数的加法运算。VHDL是一种硬件描述语言,允许开发者描述数字系统的结构和行为,以便在 FPGA 或 ASIC 上进行仿真和实现。

1)设计任务与要求:

实验要求利用基础的数字电路理论,用VHDL编写代码来设计一个4位全加器。这个全加器不仅要完成加法运算,还需要能够检测是否有进位(溢出)。4位全加器由4个1位全加器构成,每个1位全加器处理输入的两位二进制数和来自上一位的进位信号。

2)总体方案设计:

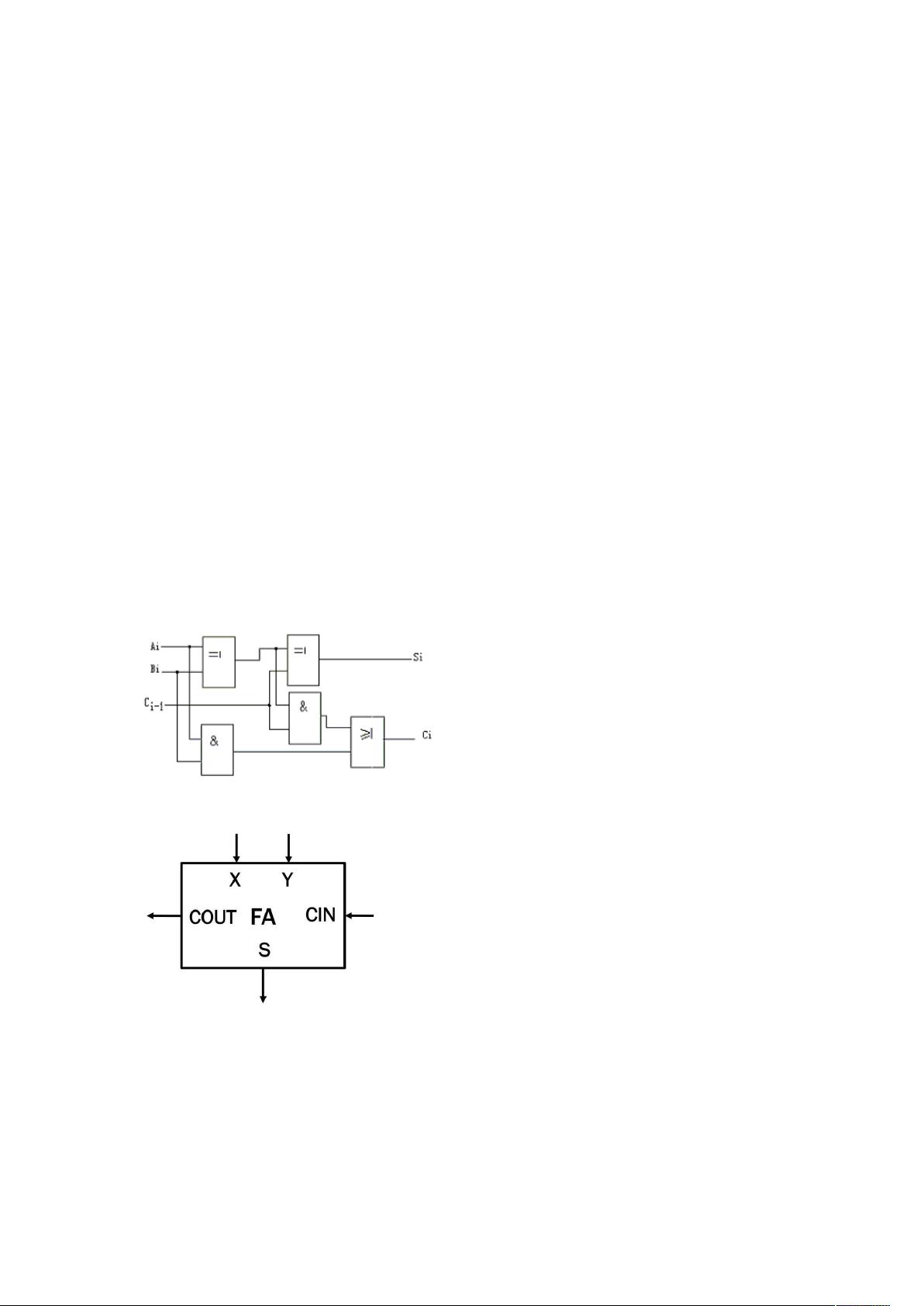

设计思路是首先构建4个独立的1位全加器,每个全加器接收两个输入位和上一位的进位信号。1位全加器的输出包括和(Sum)以及进位(Carry Out),这些输出将作为下一位全加器的输入。最终,4个全加器的和信号组合成4位的结果,而最高位的进位信号则表示整个4位加法运算的进位情况。设计者选择了直接实例化并连接4个全加器的方案,因为对于4位全加器来说,这种方法更直观,同时也避免了不必要的复杂性。

3)具体电路设计:

全加器的内部逻辑包括多个与非门(AND-NOT)和或非门(OR-NOT)组合,用于计算和进位。通过真值表和逻辑表达式可以得到全加器的完整逻辑设计。在4位全加器的设计中,每个1位全加器的输出和进位信号连接到下一个全加器的输入,最后通过异或门检测最高位和次高位的输出,以确定是否有溢出。

VHDL代码段展示了实体(entity)"Add4"的定义,它有4位输入A和B,1位进位输入Ci,4位输出S(和)和1位进位输出Co。内部使用了信号(signals)S, C, X, Y 和 Cii,以及一个名为FA的组件,该组件代表1位全加器。通过实例化FA并使用portmap映射输入和输出,将各个1位全加器连接起来,完成了4位全加器的设计。

这个实验报告提供了一个清晰的步骤,展示了如何使用VHDL来实现数字逻辑电路,对于理解和应用数字电路设计原理非常有帮助。同时,它也突显了VHDL在现代电子设计自动化(EDA)中的重要作用,使得复杂的数字系统设计变得更为简洁和高效。

2009-09-23 上传

2010-04-30 上传

2010-06-08 上传

点击了解资源详情

点击了解资源详情

2023-05-30 上传

2020-06-28 上传

2022-09-20 上传

2015-01-07 上传

slippin930

- 粉丝: 0

- 资源: 1

最新资源

- 一款简约美观的动态搜索框

- fliqlo-仿mac的锁屏时钟.zip

- cpp代码-160.4.1.3

- dotfiles:这些是我的点文件,配置

- pythonVariousTests

- Unending-Staircase:Unity中的一个虚拟现实项目。 玩家可以在VE中向上或向下无级爬楼梯

- React_bootstrap

- 大数据-倒闭企业大数据分析项目-DeathCompany.zip

- Veena-finance

- latex-workshop:针对语言学家的LaTeX研讨会材料

- lightning_gan_zoo:使用pytorch闪电和hydra配置实现的GAN模型

- matlab由频域变时域的代码-lte-sidelink:左侧链接

- TheMammoth_Public:猛mm象的公共资源

- ReactNativeTest

- c代码-递归计算斐波那契函数前n项和

- 火车票系统后端(区间票) SSM(JAVA) Oracle.zip