FPGA实现PCI-Express:高速差分信号与通信时序解析

"基于FPGA的PCI-Express(PCIe)总线设计着重于高速串行总线的开发和架构实现。本文将详细探讨PCIe技术、基本I/O概念,特别是差分信号的优势及其在高速通信中的应用。同时,我们将讨论不同类型的时序模型,包括系统同步、源同步和自同步,以及它们在FPGA设计中的具体应用和挑战。"

PCIe技术是当前广泛使用的高速接口标准,它基于点对点连接,提供了比传统PCI更高的带宽和更低的延迟。PCIe总线设计在FPGA中实现,能够充分利用FPGA的灵活性和并行处理能力,构建高性能的数据传输通道。

差分信号是PCIe技术的基础,相较于传统的单端信号,它具有更强的抗干扰能力,能有效抑制电磁干扰(EMI),并提供更精确的时序定位。这种信号传输方式在高速通信中至关重要,因为它可以显著提高信号质量,确保数据在长距离传输时的稳定性。

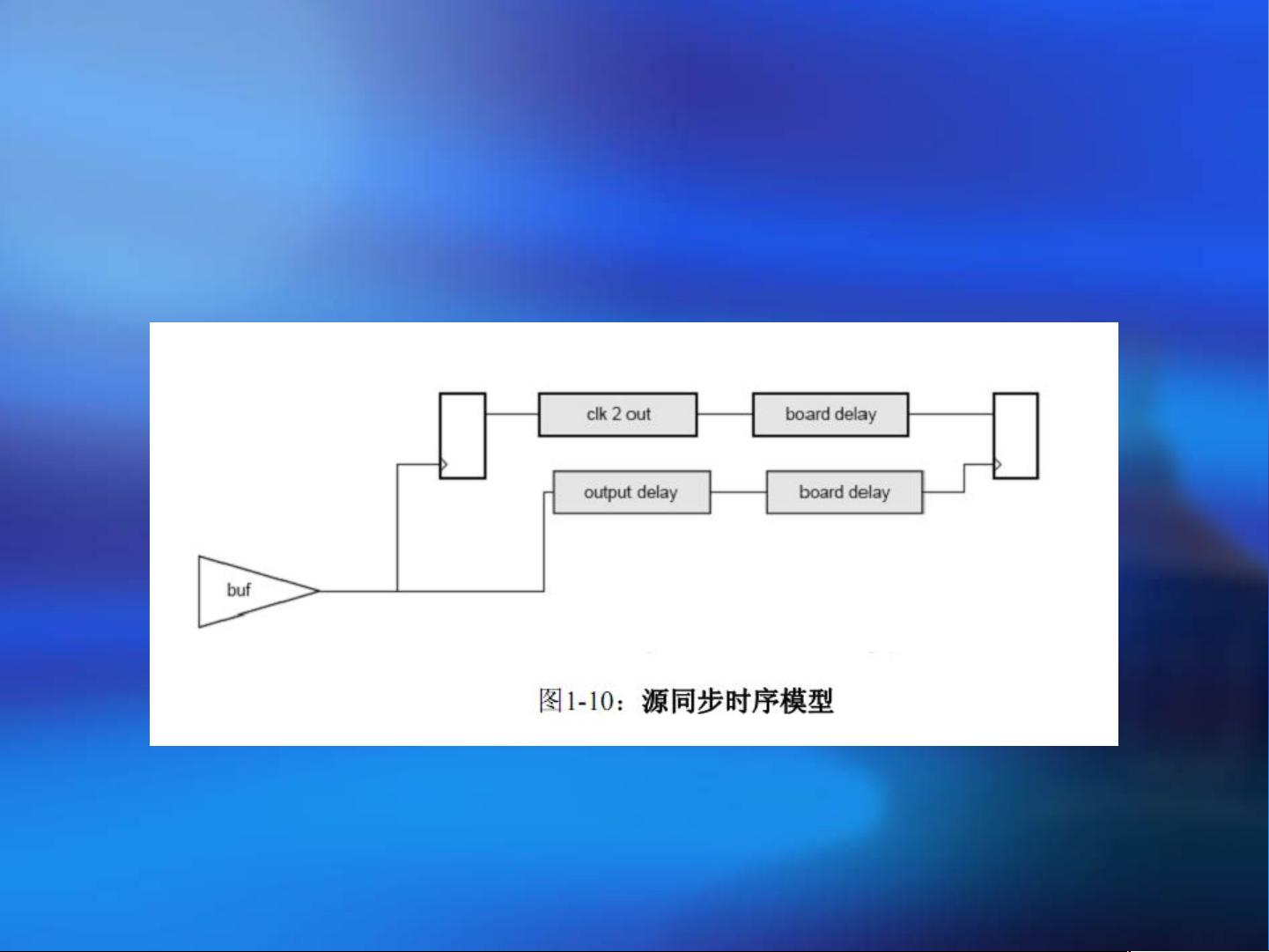

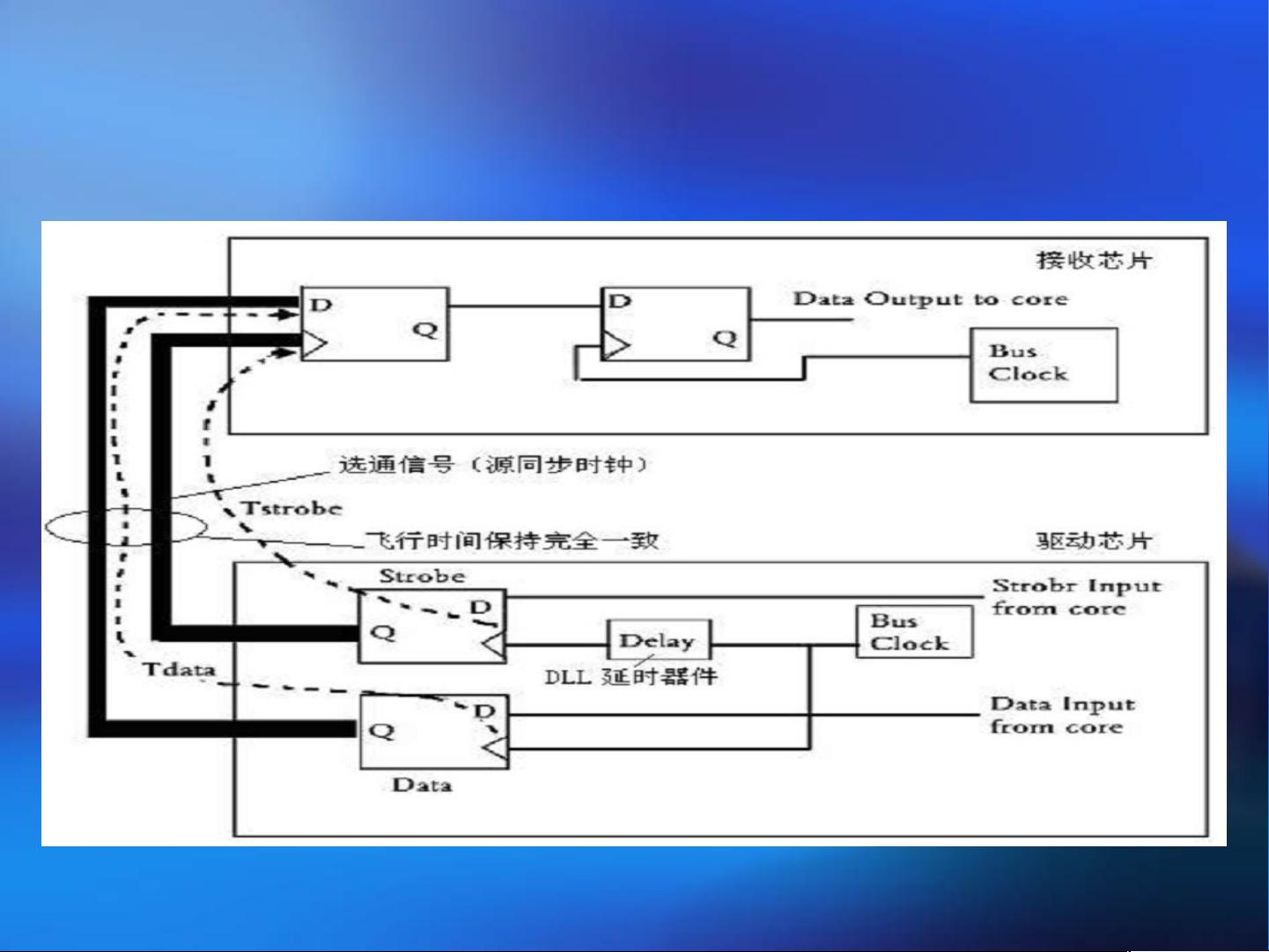

在时序模型方面,系统同步、源同步和自同步是关键的概念。系统同步模式下,驱动端和接收端共享同一时钟源,简化了时序管理。然而,随着传输速度的提升,源同步成为一种解决方案,它通过发送时钟副本与数据一起传输,以应对延时问题。尽管源同步可以简化时序参数,但会增加时钟域的数量,带来额外的时序约束和分析困难,尤其是在大型并行总线设计中。

自同步是另一种解决方案,它不依赖于共享时钟,而是通过数据流中的时钟信息进行同步。自同步接口通常包含并串转换、串并转换和时钟数据恢复(PLL)等组件。并串转换器使用可装载移位寄存器和回转选择器来处理数据,而串并转换则负责将串行数据转化为并行数据,以供FPGA内部逻辑使用。

基于FPGA的PCIe总线设计是一项复杂而关键的任务,涉及到高速信号处理、时序管理等多个领域。理解并掌握这些技术要点,能够帮助开发者优化系统性能,降低设计风险,并实现高效的数据传输。在实际设计过程中,需要根据具体需求和硬件限制灵活选择合适的同步策略,以达到最佳的系统性能和可靠性。

点击了解资源详情

143 浏览量

点击了解资源详情

点击了解资源详情

2021-02-03 上传

116 浏览量

2021-07-13 上传

点击了解资源详情

qiguangli0214

- 粉丝: 0

- 资源: 3

最新资源

- 易语言迷你SPY

- 03.2020保健品行业洞察及重点公司推荐.rar

- 随风资源互动共享系统 v1.1

- training2020

- openstad-react-admin

- 衡量其子项大小的小部件。-JavaScript开发

- 易语言远程控制本地控制台

- ios记忆力翻牌小游戏源码.rar

- docker-ejtserver:基于Alpine Linux的EJT许可证服务器映像

- 42nd-at-threadmill:SIMD加速的并发哈希表

- Arduino入门级DIY项目教程:绚丽五彩的智能IQ灯制作-电路方案

- project001:我的第一个项目

- Back_back2

- Discuz! 高贵典雅模板

- csso:具有结构优化功能CSS缩小器

- Cuomotype